# AM3517 SOM-M2 Design Checklist

**Application Note 481**

Logic PD // Products Published: May 2011

Last revised: September 1, 2016

## Abstract

This application note provides a list of items to verify when designing the AM3517 SOM-M2 into an embedded system. Reviewing this checklist prior to releasing design files and software for production can help reduce the probability of future board spins.

This document contains valuable proprietary and confidential information and the attached file contains source code, ideas, and techniques that are owned by Logic PD, Inc. (collectively "Logic PD's Proprietary Information"). Logic PD's Proprietary Information may not be used by or disclosed to any third party except under written license from Logic PD, Inc.

Logic PD, Inc. makes no representation or warranties of any nature or kind regarding Logic PD's Proprietary Information or any products offered by Logic PD, Inc. Logic PD's Proprietary Information is disclosed herein pursuant and subject to the terms and conditions of a duly executed license or agreement to purchase or lease equipment. The only warranties made by Logic PD, Inc., if any, with respect to any products described in this document are set forth in such license or agreement. Logic PD, Inc. shall have no liability of any kind, express or implied, arising out of the use of the Information in this document, including direct, indirect, special or consequential damages.

Logic PD, Inc. may have patents, patent applications, trademarks, copyrights, trade secrets, or other intellectual property rights pertaining to Logic PD's Proprietary Information and products described in this document (collectively "Logic PD's Intellectual Property"). Except as expressly provided in any written license or agreement from Logic PD, Inc., this document and the information contained therein does not create any license to Logic PD's Intellectual Property.

The Information contained herein is subject to change without notice. Revisions may be issued regarding changes and/or additions.

© Copyright 2016, Logic PD, Inc. All Rights Reserved.

i

# **Revision History**

| REV | EDITOR   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | APPROVAL | DATE     |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|

| Α   | SK       | -Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | JCA      | 05/06/11 |

| В   | BSB, JCA | -Section 2.1: Added suggestion in list number 2 to add non-populated pads for an external pull-up and pull-down resistor in case internal resistors are not adequate; -Section 2.3: Added list number Error! Reference source not found. regarding need to tie RSRV02 to 3.3V_or1.8V reference voltage; -Section 2.4: Added list number 7 regarding TRS3386 RS-232 transceiver; -Section 2.11: Added list number 3 regarding MMC_CMD and MMC_DATx signals; -Section 2.12: Added list number 3 regarding requirement for 3.3V domain power 10 ohm pull-ups connecting to the Ethernet magnetics; added list number 4 regarding common mode capacitors for ETHER_TX+, ETHER_TX-, ETHER_RX+, and ETHER_RX- signals; -Section 6: Added updated link for the TI AM35x Schematic Checklist wiki page | SO       | 03/18/13 |

| С   | so       | -Added Section 2.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | JA, RAH  | 06/19/13 |

| D   | BSB      | -Removed Section 2.3: number 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NK       | 9/1/2016 |

# **Table of Contents**

| 1 | l Introduction1 |                                       |  |  |  |  |  |

|---|-----------------|---------------------------------------|--|--|--|--|--|

| 2 |                 |                                       |  |  |  |  |  |

| 2 | .1              | Clocks                                |  |  |  |  |  |

| 2 | .2              | Reset                                 |  |  |  |  |  |

| 2 | .3              | Power                                 |  |  |  |  |  |

| 2 | .4              | Level Shifters                        |  |  |  |  |  |

| 2 | .5              | Peripheral Interfaces                 |  |  |  |  |  |

| 2 | .6              | GPIO                                  |  |  |  |  |  |

| 2 | .7              | LCD                                   |  |  |  |  |  |

| 2 | .8              | Debug                                 |  |  |  |  |  |

| 2 | .9              | I/O Interface                         |  |  |  |  |  |

| 2 | .10             | USB OTG VBUS                          |  |  |  |  |  |

| 2 | .11             |                                       |  |  |  |  |  |

| 2 | .12             | · · · · · · · · · · · · · · · · · · · |  |  |  |  |  |

| 2 | .13             | McBSP                                 |  |  |  |  |  |

| 2 | .14             | Audio                                 |  |  |  |  |  |

|   |                 | out Checklist4                        |  |  |  |  |  |

| 3 | .1              | USB                                   |  |  |  |  |  |

| 3 | .2              | Ethernet                              |  |  |  |  |  |

| 3 | .3              | Decoupling Caps                       |  |  |  |  |  |

| 3 | .4              | Baseboard Connectors and Silkscreen   |  |  |  |  |  |

| 3 | .5              | SOM-M2 Placement                      |  |  |  |  |  |

| 4 | Sof             | tware Checklist                       |  |  |  |  |  |

| 5 |                 |                                       |  |  |  |  |  |

| 6 |                 |                                       |  |  |  |  |  |

| 7 | Summary6        |                                       |  |  |  |  |  |

### 1 Introduction

When using the AM3517 SOM-M2 in an embedded system, reviewing some specifics during the design phases can minimize or even eliminate future board spins. Information provided in this application note should be reviewed prior to releasing a design for fabrication and assembly. It is also critical that software teams review Sections 4 and 5 to ensure a trouble-free first board boot.

## 2 Schematic Checklist

Items in this section should be reviewed by the system designer prior to releasing the design for layout.

## 2.1 Clocks

- 1. Verify that series termination is available for all clock signals that do not have internal drive strength control.

- 2. The SYS\_CLKREQ (J3.16) signal has an internal, software selectable pull-up/down resistor. When SYS\_CLKREQ is used as an output to control an external oscillator or other clock source, add non-populated pads for an external pull-up and pull-down resistor. The non-populated pads are a contingency plan in case the internal resistors are not adequate. The pull-up pad will be available when using SYS\_CLKREQ with active low polarity. The pull-down pad will be available when using SYS\_CLKREQ with active high polarity.

#### 2.2 Reset

uP\_RESWARMn (J3.52) is an open collector only pin. Do not place a pull-up resistor on this pin.

#### 2.3 Power

- Verify all power and ground signals are connected correctly and are at the correct voltage level.

- 2. Verify the regulators provide sufficient current demands.

- 3. Pin J1.37 selects between a 3.3V or 1.8V supply. If left floating, a 3.3V supply is implied.

#### 2.4 Level Shifters

- 1. Verify if any of the signals or buses used from the AM3517 SOM-M2 require level shifting for your specific design. In general, the signals in the AM3517 SOM-M2 can be switched between 1.8V and 3.3V.

- 2. Verify the correct reference voltage from the AM3517 SOM-M2 is used for signal-level shifting or pull-ups.

- 3. Verify that the reference voltage is not used as a power source.

- 4. Verify that the direction signal has the proper direction control.

- 5. Verify that unused input signals to the level shifter are tied per the level-shifter specification and are not left floating.

- 6. For interface signals that have different directions (e.g., RX and TX), verify that the level shifters also have different direction signals.

- 7. The TRS3386 RS-232 transceiver is no longer qualified to work at 1.8V. The TRS3253 is an alternative device that does support 1.8V operation.

## 2.5 Peripheral Interfaces

Verify peripheral interface connections, such as USB, serial, and SD Card, are equivalent to those on the AM3517 EVM or experimenter Development Kit baseboard.

#### 2.6 **GPIO**

- 1. Verify the signal selected to be a GPIO is actually available as an alternative function or is a dedicated GPIO, GPI, or GPO function needed for the design.

- Verify that no contention occurs on GPIO signals during reset and low-power mode states.

- 3. Verify that signals designated as GPIO have reset states with the desired direction and level.

- 4. Verify GPIO signals in Table 2.1 are used as input only (GPI) signals.

| uP GPIO Signal | SOM-M2 Signal  | SOM-M2 Pin |

|----------------|----------------|------------|

| GPIO_99        | CCDC_D0        | J3.30      |

| GPIO_100       | CCDC_D1        | J3.32      |

| GPIO_112       | RMII_TXD1      | N/A        |

| GPIO_113       | RMII_TXEN      | N/A        |

| GPIO_114       | RMII_50MHZ_CLK | N/A        |

Table 2.1: GPI Signals

#### 2.7 LCD

The recommended LCD interface is to support 16-bit (5:6:5) color. Contact Logic PD¹ about supporting other color depths.

## 2.8 Debug

- Serial: Logic PD recommends all designs have a debug serial port. This port is used for terminal access to the Linux PSP. UART3\_TX (J1.97) and UART3\_RX (J1.99) are the dedicated debug port signals used on the AM3517 SOM-M2.

- 2. JTAG: The JTAG interface and voltage required for your tools may be different than those used on the AM3517 EVM or eXperimenter Development Kit baseboard. Verify that the JTAG connector interface for your design will interface to the emulator that is planned for software development.

- 3. Ethernet: Logic PD recommends putting down a WLAN Ethernet port on the first phase of baseboards: this port can be used for development and download purposes.

- 4. Serial-to-USB: Logic PD recommends copying this reference from the AM3517 EVM or eXperimenter Development Kit baseboard only if the host PC does not have a RS232 serial interface.

- 5. Reset: Logic PD recommends designing in a de-bounced RESPWRONn (J1.29) button to the AM3517 SOM-M2 to aid in debug.

#### 2.9 I/O Interface

Verify that any signal driven from the AM3517 SOM-M2 has no more than one load. A buffer must be used if driving more than one load from the AM3517 SOM-M2 in your design.

1

<sup>&</sup>lt;sup>1</sup> http://support.logicpd.com/support/askaquestion.php

## 2.10 USB OTG VBUS

Use Table 2.2 for proper decoupling capacitance values on USB0\_VBUS for different operation modes.

Operation Mode

Decoupling Value

Notes

OTG Operation

1-6.5 uF

—

Leave USB0\_DRVVBUS and USB0\_ID as no connect

Device Operation

< 10 uF</td>

no connect

Host Operation

> 150 uF

—

Table 2.2: Decoupling Capacitance Values

## 2.11 Secure Digital/MicroSD

- 1. When Secure Digital (SD) or MicroSD cards are used in a system design, signal J1.73 (MMC1\_D5) is used as a card detect signal.

- 2. Signal J1.71 (MMC1\_D4) is also used as a write protect signal.

- 3. MMC\_CMD, MMC\_DATx: 10K pull-ups are needed on each signal, unless using it in SDIO mode (e.g., connected to a WLAN device) or using a TXS0108 similar to the AM3517 EVM Development Kit design. Be sure to pull up to the MMC voltage domain.

## 2.12 Ethernet Magnetics

- The Ethernet controller on the AM3517 SOM-M2 is an SMSC LAN8710 component. SMSC provides <u>Application Note 8.13</u><sup>2</sup> that lists suggested magnetics for use with their SMSC LANxxxx components.

- 2. When connecting the magnetic to the SMSC LAN8710 on the AM3517 SOM-M2, the following connections must be followed to match the SMSC LAN8710 reference design:

- Separate the transmit and receive center taps.

- Tie a 10 ohm (1/8W 1%) resistor between 3.3V and the center tap signals of the magnetic.

- □ Connect a 0.22 uF (0805) capacitor from the center tap signal to digital ground.

- 3. Verify that the 10 ohm resistors used to pull the transmit center tap and the receive center tap up to 3.3V do not receive power prior to the AM3517 module. This can be done by gating the 3.3V power to the 10 ohm pull-up resistors using either the uP\_RESETn signal or the 3.3V\_or\_1.8V signal to signify a PGOOD. The 3.3V\_or\_1.8V reference should not be used to power these resistors directly.

- 4. Common mode capacitors are recommended for the ETHER\_TX+, ETHER\_TX-, ETHER\_RX+, and ETHER\_RX- signals. The capacitors should be 10 pF 22 pF to digital ground. They can be marked as Do Not Populate (DNP) and would provide EMI rejection if the problem should arise. Care must be taken to ensure this does not break the impedance and trace length matching for these signals in layout.

#### 2.13 McBSP

The AM3517 SOM-M2 can support up to five McBSP ports. Of the five McBSP ports, McBSP3 and McBSP4 are connected to the wireless front-end module.

2

<sup>&</sup>lt;sup>2</sup> http://www.smsc.com/Downloads/SMSC/Downloads\_Public/Application\_Notes/an813.pdf

#### **2.14** Audio

The TLV320 xOUT signals do not support software-based volume control. Route the HPxOUT signals if software-based volume control is needed. If the xOUT signals must be used, consider an external adjustable amplifier.

# 3 Layout Checklist

Items listed in this section should be reviewed by the layout designers prior to releasing the Gerber design files for board production.

#### 3.1 USB

Verify that the USB differential pairs listed below have an impedance match of 90 ohms:

- uP USB0 DM/uP USB0 DP

- uP\_USB1\_DM/uP\_USB1\_DP

#### 3.2 Ethernet

Verify that the Ethernet differential signals listed below have an impedance match of 100 ohms:

- ETHER RX+/ETHER RX-

- ETHER\_TX+/ETHER\_TX-

## 3.3 Decoupling Caps

Decoupling caps must be placed as close as possible to the targeted component.

#### 3.4 Baseboard Connectors and Silkscreen

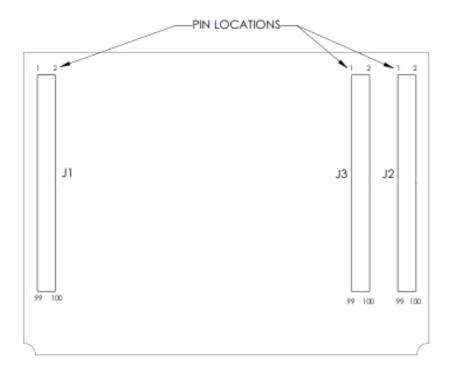

1. Verify that baseboard connectors are positioned in the correct order where J1 and J2 are the outside connectors. The silkscreen should display pins 1, 2, 99, and 100 for each connector to show their orientation on the board. See Figure 3.1.

Figure 3.1: Recommended Baseboard Footprint

- 2. Logic PD recommends that the silkscreen display dots for every ten J1/J2/J3 connector edge pins (e.g., 10, 20, 30, ... 100).

- 3. Review all silkscreen markings to make sure nothing is covered due to vias or part placement.

#### 3.5 SOM-M2 Placement

Verify sufficient baseboard space exists in terms of height, width, and length for the AM3517 SOM-M2 per the recommended baseboard footprint in Appendix A of the <u>AM3517 SOM-M2 Hardware Specification</u><sup>3</sup>.

## 4 Software Checklist

Items listed in this section should be reviewed by the software engineer prior to releasing software for testing.

- 1. Pull-ups/downs: Verify that software configures all signals that are not pull-ups, pull-downs, or present in hardware.

- 2. Power Management: Verify the targeted Board Support Package (BSP) has the required power management support to meet your system requirements.

<sup>&</sup>lt;sup>3</sup> http://support.logicpd.com/downloads/1257/

# 5 Board Bring-Up Checklist

Items listed in this section can aid in system bring-up. Check the items in the order provided below.

- 1. Power: Verify adequate power is applied to MAIN BATT IN.

- 2. Reset: Verify the uP\_RESETn signal goes high.

- 3. UART3: Verify that serial output from the debug serial port is operational (the serial port must be set at: baud rate: 115200; data: 8-bit; parity: none; stop; 1-bit; flow control: none).

### 6 TI AM3517 Processor Schematic Checklist

Additional AM3517 processor schematic checklist information can be found on the TI <u>AM35x</u> <u>Schematic Checklist wiki page</u>. <sup>4</sup> Though information provided in the TI checklist may not apply specifically to Logic PD hardware, it can be used as a reference. If there are any conflicts between the TI checklist and this Logic PD design checklist, please contact Logic PD.

## 7 Summary

This application note is provided as a guide to use during development and bring-up of your platform. The ideas provided within this document may help reduce debug time and limit or eliminate future re-spins of your embedded system. Information provided in the *AM3517 SOM-M2 Hardware Specification* or any specification document for onboard components takes precedence over the information within this application note.

4

<sup>&</sup>lt;sup>4</sup> http://processors.wiki.ti.com/index.php/AM35x\_Schematic\_Checklist