### **REVISION HISTORY**

| REV | EDITOR                                                  | REVISION DESCRIPTION                         | APPROVAL | DATE     |  |

|-----|---------------------------------------------------------|----------------------------------------------|----------|----------|--|

| 1   | Paul Mueller                                            | First Draft Version                          | PGM      | 04/29/03 |  |

| Α   | Paul Mueller                                            | ueller Production Release                    |          | 05/02/03 |  |

| В   | Himanshu Khadilkar                                      | Editing                                      | HK       | 06/23/03 |  |

| С   | James Wicks                                             | Added mode line description note             | JW       | 09/19/03 |  |

| D   | James Wicks Sections 2.7.2 & 4.2.1: clarification; edit |                                              | JW       | 10/30/03 |  |

| E   | Erik Reynolds,<br>Michael Anderson,<br>James Wicks      | Edit to coincide with the LH75401-11 Release | ECR      | 01/14/04 |  |

| REV | EDITOR       | REVISION DESCRIPTION                                                                                                                                                                                                                                                                                                     | SCHEMATIC REV                                            | APPROVAL | DATE     |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------|----------|

|     |              | Corrected typo in Section 1.7.2 where the DC Core Supply Active Current was mistakenly listed as "T70"; Corrected Hirose PNs in Section 6.1 to reflect available parts; Added second Important Note to Section 6.1; General grammatical and formatting changes; Corrected Figure Numbers 2.4 and 3.2 to follow numbering | <u>LH75401-10</u><br>80000132 Rev A<br><u>LH75401-11</u> |          |          |

| F   | Jed Anderson | scheme                                                                                                                                                                                                                                                                                                                   | 80000227 Rev A01                                         | JCA      | 11/15/06 |

Please check  $\underline{www.logicpd.com}$  for the latest revision of this manual, erratas, and additional application notes.

# **Table of Contents**

| 1 |                | iction                                                 |    |

|---|----------------|--------------------------------------------------------|----|

|   | 1.1 Pro        | oduct Brief                                            | 6  |

|   | 1.2 Ac         | ronyms                                                 | 7  |

|   |                | chnical Specification                                  |    |

|   |                | rd Engine Advantages                                   |    |

|   |                | rd Engine Interface                                    |    |

|   | 1.5 Ca         | 75401-10/11 Card Engine Block Diagram                  | 5  |

|   | 1.6 LH         | 75401-10/11 Card Engine Block Diagram                  | 10 |

|   |                | ectrical, Mechanical, and Environmental Specifications |    |

|   | 1.7.1          | Absolute Maximum Ratings                               | 11 |

|   | 1.7.2          | Recommended Operating Conditions                       |    |

| 2 | Electri        | cal Specification                                      | 12 |

|   | 2.1 Mid        | croController                                          | 12 |

|   | 2.1.1          | LH75401 Microcontroller                                |    |

|   | 2.1.2          | LH75401 Microcontroller Block Diagram                  |    |

|   |                | DCKS                                                   |    |

|   |                | emory                                                  |    |

|   |                |                                                        |    |

|   | 2.3.1          | SRAM                                                   |    |

|   | 2.3.2          | Direct Memory Access (DMA)                             |    |

|   | 2.3.3          | NOR Flash                                              |    |

|   | 2.3.4          | CompactFlash (memory-mapped mode only)                 |    |

|   | 2.4 10         | /100 Ethernet Controller                               | 15 |

|   | 2.5 Au         | dio Codec                                              | 15 |

|   | 2.6 Vid        | deo Interface                                          | 16 |

|   |                | rial Interface                                         |    |

|   | 2.7.1          | UARTA                                                  |    |

|   | 2.7.2          | UARTB                                                  |    |

|   | 2.7.2          | UARTC                                                  |    |

|   |                |                                                        |    |

|   | 2.7.4          | SPI                                                    |    |

|   |                | N                                                      |    |

|   |                | uch Interface                                          |    |

|   | 2.10 Ge        | eneral Purpose Analog & Digital I/O                    | 18 |

|   |                | PLD                                                    |    |

|   | 2.12 Se        | rial EEPROM Interface                                  | 18 |

|   |                | pansion Options                                        |    |

| 3 |                | n Integration                                          |    |

| • |                | nfiguration                                            |    |

|   |                | sets                                                   |    |

|   |                |                                                        |    |

|   | 3.2.1<br>3.2.2 |                                                        |    |

|   |                |                                                        |    |

|   |                | errupts                                                |    |

|   |                | AG Debugger Interface                                  |    |

|   | 3.5 Po         | wer Management                                         |    |

|   | 3.5.1          | System Power Supplies                                  | 21 |

|   | 3.5.2          | Peripherals                                            |    |

|   | 3.5.3          | System Power Management                                |    |

|   | 3.5.4          | Microcontroller                                        |    |

|   |                | D Considerations                                       |    |

| 4 |                | y & I/O Mapping                                        |    |

| * |                |                                                        |    |

|   |                | AM Memory Map                                          |    |

|   |                | ternal Static Memory Map                               |    |

| _ | 4.2.1          | Card Engine Static Memory Map Description              |    |

| 5 |                | scriptions & Functions                                 |    |

|   | 5.1 J1         | C Connector SO-DIMM 144-Pin Descriptions               | 27 |

|   |                |                                                        |    |

|   | 5.2 | J1A Expansion Connector Pin Descriptions       | 32 |

|---|-----|------------------------------------------------|----|

|   | 5.3 | J1B Expansion Connector Pin Description        | 35 |

|   |     | Multiplexed Signal Trade-Offs                  |    |

|   |     | 1.1 J1C Connector SO-DIMM 144-Pin Multiplexing |    |

|   |     | 4.2 J1A Expansion Connector Pin Multiplexing   |    |

|   |     | 1.3 J1B Expansion Connector Pin Multiplexing   |    |

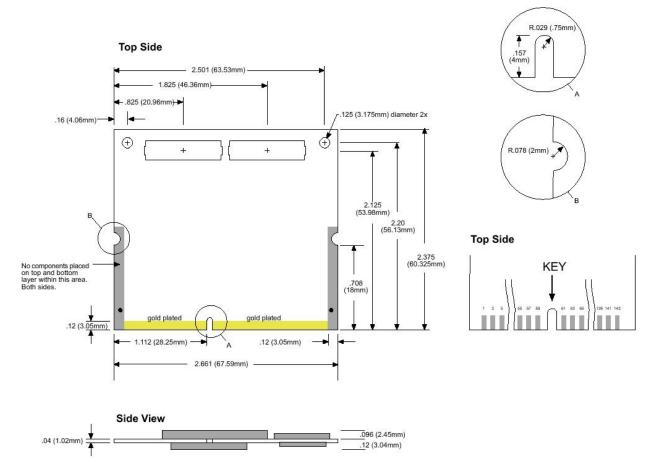

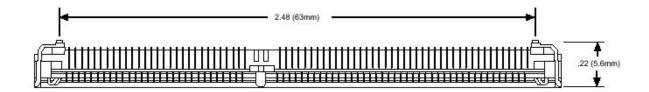

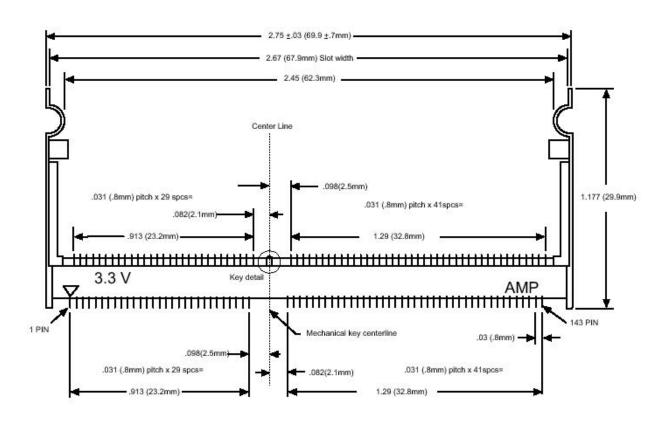

| 6 |     | echanical Specifications                       |    |

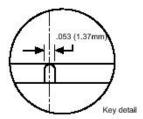

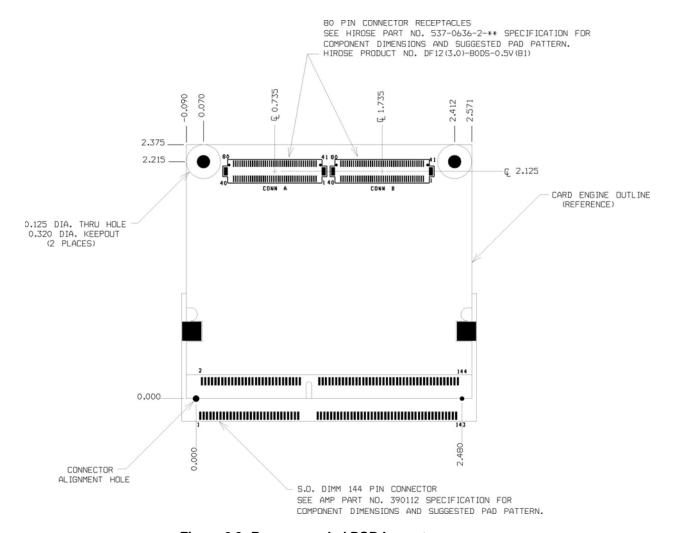

|   |     | Interface Connectors                           |    |

# **Table of Figures**

| Figure 1.1: Card Engine Advantages                  | 9  |

|-----------------------------------------------------|----|

| Figure 1.2: LH75401-10/11 Card Engine Block Diagram |    |

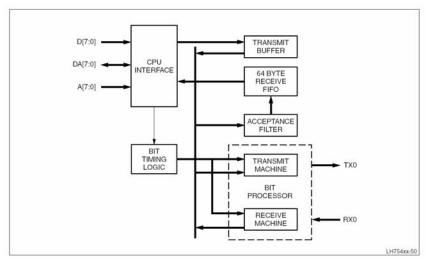

| Figure 2.1: LH75401 Microcontroller Block Diagram   |    |

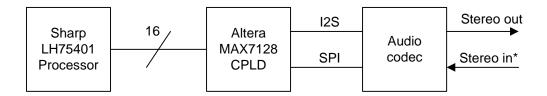

| Figure 2.2: Audio CODEC Block Diagram               | 15 |

| Figure 2.3 CAN Controller Block Diagram             | 17 |

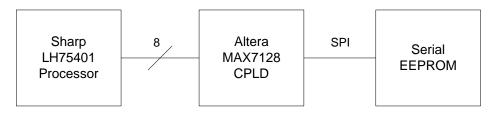

| Figure 2.4: Serial EEPROM Block Diagram             | 18 |

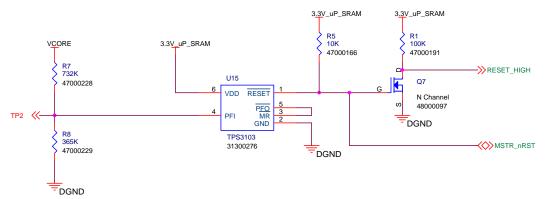

| Figure 3.1: Reset Circuit                           | 19 |

| Figure 3.2: Power Plane Diagram                     | 22 |

| Figure 4.1: LH75401 Card Engine General Memory Map  | 25 |

| Figure 6.1: Card Engine Mechanical Drawing          |    |

| Figure 6.2: SODIMM Connector Specification          | 41 |

| Figure 6.3: Recommended PCB Layout                  | 42 |

|                                                     |    |

# **LH75401 CARD ENGINE**

The LH75401 Card Engine is a compact, product-ready hardware and software solution for developing embedded products with less time, less cost, less risk ... more innovation.

#### **CARD ENGINE ADVANTAGE**

- Reduce Time to Market

- → 6 to 9 month savings typical

- Product-Ready Hardware Platform

- Production Quality Software

- Bootloader/Monitor

- Board Support Packages

- Supports other operating systems

- Engineering Support

#### ORDERING INFORMATION

Zoom<sup>™</sup> Starter Development Kit (Model # SDK-LH75401-11-0204)

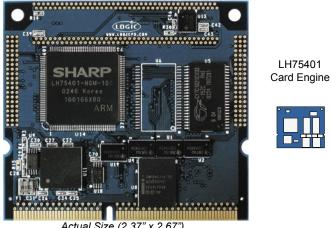

### The LH75401 Card Engine is a complete System on Module offering essential features for handheld and embedded networking applications in the industrial, consumer, and medical markets. The use of custom peripheral boards makes the Card Engine the ideal foundation for OEMs developing handheld and compact products. The Card Engine provides a common reference pin-out on its expansion connectors, which enables customers to easily scale to next generation micro controller Card Engines when new funtionality or performance is required.

Actual Size (2.37" x 2.67")

- Processor Sharp LH75401 16/32 bit ARM7TDMI RISC micro processor running up to 70 MHz

- **SDRAM Memory** Up to 2 Mbytes

- Flash Memory Up to 8 Mbytes on board

- **Display** Programmable color LCD controller

- Built in driver supports up to 320 x 240 (QVGA) x 12 bit color

- Supports STN, Color STN, HR-TFT, AD-TFT, TFT

- Touch Screen Processor Integrated four or five wire resistive touch screen controller

- Network Support 10/100 BASE-T Ethernet controller (application/debug)

- SMSC LAN 91C111 (MAC & PHY)

- Audio Audio Codec Stereo Output (TI TLV320DAC23)

- PC Card Expansion Compact Flash type 1 card (memory storage only)

- Serial Ports 3 X UARTS

- 2 X 16C550 like, standard UARTS

- 1 CAN Version 2.0b or 1 82510 UART

- SSP Supports either Motorola SPI™, National Semiconductor MICROWIRE™, TI SSI

- **GPIO** Programmable depending on peripheral requirements

- **Software**

- LogicLoader™ (bootloader/monitor)

- Mechanical

- Compact Size: 2.37"(60.2 mm) long x 2.67"(67.8 mm) wide x 0.17"(4.4 mm) high

- 144 pin SODIMM connector for connection to custom peripheral board

- Two high density 80-pin expansion connectors for peripheral access

- **Application Development Kits**

- Zoom™ Starter Development Kit (Model # SDK-LH75401-11-0204)

#### **CUSTOMER SUPPORT**

Logic provides technical support for Application Development Kits. Various support packages are available: contact us for more information.

#### **CONTACT**

For more information on our EmbeddedProduct Solutions. please contact Logic Sales at www.logicpd.com or 612.672.9495.

Final

Product

Custom

Base Board

### 1.2 Acronyms

ADC Analog to Digital Converter

AHB Advanced Hardware Bus

BSP Board Support Package

CPLD Complex Programmable Logic Device

DAC Digital to Analog Converter

DC Direct Current

DMA Direct Memory Access

DRAM Dynamic Random Access Memory

ENDEC Encoder Decoder

ESD Electro Static Dissipative

FET Field Effect Transistor

FIFO First In First Out

FIQ Fast Interrupt Request

GPIO General Purpose Input Ou

GPIO General Purpose Input Output HAL Hardware Abstraction Layer

IC Integrated Circuit

IO Input Output

LCD Liquid Crystal Display

LOLO LogicLoader™

NC No Connect

PLL Phase Lock Loop

PMOS P Metal Oxide Semiconductor

RTC Real Time Clock

SDRAM Synchronous Dynamic Random Access Memory

SRAM Static Random Access Memory SSP Synchronous Serial Port TTL Transistor Transistor Logic

UART Universal Asynchronous Receive Transmit

VIC Vectored Interrupt Controller

#### 1.3 Technical Specification

Please refer to the following component specifications and data sheets.

LH75401-10/11 IO Controller Specification

LogicLoader<sup>TM</sup> User's Manual

LH75401 Universal Microcontroller User's Guide Altera MAX 7000A CPLD data sheet (EPM7128)

Altera Device Package Information data sheet

Altera Ordering Information

Texas Instruments TLV320DAC23 data manual

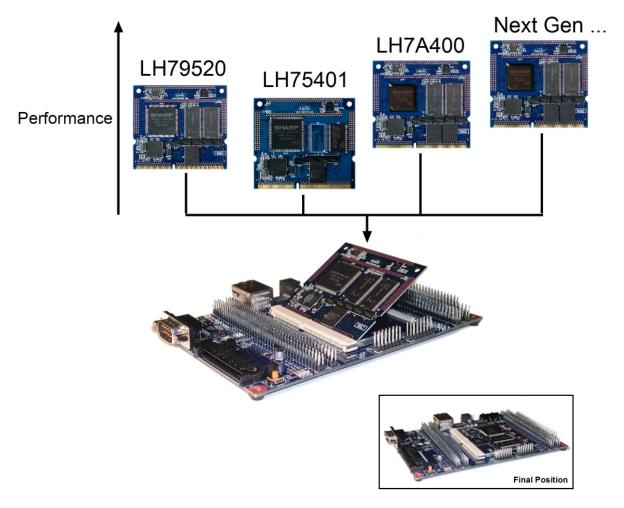

#### 1.4 Card Engine Advantages

Logic's Card Engines accelerate your products time to market. In addition, the Card Engines provide the following advantages:

- Product Ready Hardware & Software solutions allow immediate application development which results in embedded product development cycle with less time, less cost, less risk, and with more innovation.

- □ Less time time to market solution allows software application development to begin immediately

- □ Less cost significantly lowers development cost

- □ Less risk complex portion of design product ready

- ☐ More Innovation Allows you to focus on your IP

- Common Card Engine Footprint (See Figure 1.1)

- Easy migration path to new processors and technology

- Provides a scaleable solution for your product family

- □ Extends product life cycle worry free component obsolescence

- Low Cost Hardware Solution Custom configurations to meet your design requirements and price points.

- Complex portion of the design complete and ready to go.

### 1.5 Card Engine Interface

The Card Engine's common interface allows you to easily migrate to new processors and technology. Logic is in constant research and development of new technologies to improve performance, lower cost and increase feature capabilities. By using the common footprint, you can leverage Logic's work without having to re-spin your product. Contact Logic sales for more information.

Figure 1.1: Card Engine Advantages

Encapsulating a significant amount of your design onto the Card Engine reduces risk of obsolescence issues. If a component on the Card Engine design becomes obsolete you don't have to re-spin your board, Logic will design for alternative part that is transparent to your product. Manufacturing also becomes much easier. Card Engines are delivered to you fully tested, making your manufacturing process simpler and less costly.

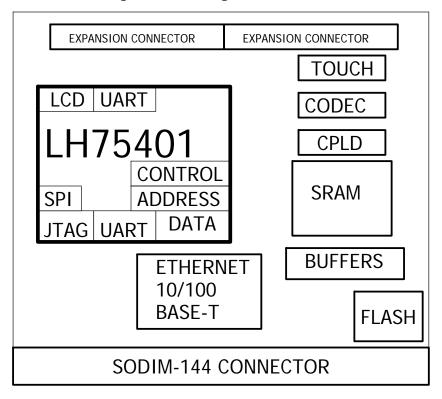

### 1.6 LH75401-10/11 Card Engine Block Diagram

Figure 1.2: LH75401-10/11 Card Engine Block Diagram

### 1.7 Electrical, Mechanical, and Environmental Specifications

#### 1.7.1 Absolute Maximum Ratings

| Parameter                           | Symbol | Rating      | unit |

|-------------------------------------|--------|-------------|------|

| DC IO and Peripheral Supply Voltage | 3.3V   | -0.3 to 4.6 | V    |

| DC Core Supply Voltage              | VCORE  | -0.3 to 2.4 | V    |

NOTE: These stress ratings are only for transient conditions. Operation at or beyond absolute maximum rating conditions may affect reliability and cause permanent damage to the Card Engine and its components.

### 1.7.2 Recommended Operating Conditions

| Parameter                           | Min  | Typical     | Max  | Unit   | Notes |

|-------------------------------------|------|-------------|------|--------|-------|

| DC IO and Peripheral Supply Voltage |      | 3.3         | 3.6  | V      | 1     |

| DC IO Supply Active Current         | TBD  | 320         | TBD  | mA     | 2     |

| DC IO Supply Standby Current        | TBD  | 300         | TBD  | mA     | 2     |

| DC IO Supply Sleep Current          | TBD  | 300         | TBD  | mA     | 2     |

| DC Core Supply Voltage              | 1.62 | 1.8         | 1.98 | V      | 1     |

| DC Core Supply Active Current       | TBD  | 40          | 70   | mA     | 2     |

| DC Core Supply Standby Current      | TBD  | 30          | 40   | mA     | 2     |

| DC Core Supply Sleep Current        | TBD  | 0           | 3    | mA     | 2     |

| Commercial Operating Temperature    | 0    | 25          | 70   | °C     |       |

| Industrial Operating Temperature    | -40  | 25          | 85   | °C     | 3     |

| Storage Temperature                 | -40  | 25          | 85   | °C     |       |

| Dimensions                          |      | 2.37 x 2.67 |      | Inches |       |

| Weight                              |      | 17          |      | Grams  | 4     |

| Connector Insertion/removal         |      | 50          |      | Cycles |       |

| Input signal High Voltage           |      | 2.0         |      | V      |       |

| Input Signal Low Voltage            |      | 0.8         |      | V      |       |

| Output Signal High Voltage          | 2.6  |             | VIO  | V      |       |

| Output Signal Low Voltage           | GND  |             | 0.4  | V      |       |

- 1. Core voltage must never exceed IO and peripheral supply voltage.

- 2. This test was performed with the 91C111 chip power disabled.

- 3. Contact Logic for more information on an industrial temperature LH75401-10/11 Card Engine

- 4. May vary depending on Card Engine configuration.

### 2 Electrical Specification

#### 2.1 MicroController

#### 2.1.1 LH75401 Microcontroller

The LH75401-10/11 Card Engine uses Sharp's highly integrated system on a chip LH75401 microcontroller. Sharp's LH75401 has a 32-bit ARM7TDMI-S RISC core. Sharp's LH75401 microcontroller is a system on a chip providing many integrated on-chip peripherals including:

- Integrated ARM7TDMI-S<sup>TM</sup> Core 32 bit ARM7TDMI<sup>TM</sup> RISC Core□

- 32 KB on-chip SRAM

- □ 16 KB Tightly Coupled Memory(TCM) SRAM

- □ 16 KB Internal SRAM

- Integrated Touchscreen Controller

- Clock and Power Management

- Eight Channel, 10-bit Analog-to-Digital Converter

- Serial Interfaces

- □ Two 16C550-type UART

- □ One 82510-type UART

- Synchronous Serial Port

- Real Time Clock (RTC)

- Three Counter/Timers

- Low Voltage Detector

- JTAG Debug interface and Boundary Scan

- Single 3.3 V Supply

- 5 V Tolerant Inputs

- 144-pin LQFP Package

- -40°C to +85°C Operating Temperature

- CAN Controller that supports CAN version 2.B

See Sharp's LH75401 Universal Microcontroller User's Guide for additional information. http://www.sharpsma.com/

**IMPORTANT NOTE:** Please see <a href="http://www.sharpsma.com/">http://www.sharpsma.com/</a> for any errata on the LH75401.

#### 14.7456 MHz 32.768 kHz 40h 40 OSCILLATOR, PLL, POWER MANAGEMENT, and REAL TIME CLOCK RESET CONTROL 76-BIT GENERAL INTERNAL PURPOSE I/O 16KB SRAM AHB ARM7TDMI-S INTERFACE I/O CONFIGURATION VECTORED INTERRUPT CONTROLLER TCM 16KB SRAM SYNCHRONOUS SERIAL PORT 4 CHANNEL DMA CONTROLLER TIMER (3) STATIC MEMORY CONTROLLER ADVANCED PERIPHERAL WATCHDOG BUS BRIDGE TIMER COLOR CAN 2 OR LCD CONTROLLER BROWNOUT UART (3) AD-TET LCD TIMING LINEAR CONTROLLER

#### 2.1.2 LH75401 Microcontroller Block Diagram

REGULATOR

Figure 2.1: LH75401 Microcontroller Block Diagram

ADVANCED HIGH

PERFORMANCE

BUS (AHB)

8 CHANNEL 10-BIT ADC TOUCH PANEL INTERFACE

LH75401-1

ADVANCED

BUS (APB)

PERPHERAL

#### 2.2 Clocks

The Sharp LH75401 processor requires a 14.7456 MHz (LH75401-10) or 20.0000 MHz (LH75401-11) crystal that is driven by the internal PLL.. This frequency is scaleable through software to generate a HCLK signal, which serves as the system clock. By using 14.7456 MHz or 20.0000 MHz crystal the exact frequencies required for proper UART operation are obtained. The 32.786 kHz crystal oscillator output is divided by 32768 to produce the 1 Hz RTC.

The LH75401 is software configurable to select between asynchronous, synchronous, and FastBus extension clocking mode. The microcontroller has a sophisticated clocking architecture and can be software programmable tailored to an application to vary the microcontroller performance, power consumption, and bus throughput. See the LH75401 Universal Microcontroller User's Guide for more details.

The LH75401-10's microcontroller core clock speed is initialized to 51.6096 MHz on the Card Engine and the Bus speed is 51.6096 MHz in the LogicLoader™. Other clock speeds can be supported and modified in software for specific user applications, such as a specific serial baud rate.

The LH75401-11's microcontroller core clock speed is initialized to 70.0000 MHz on the Card Engine and the Bus speed is 70.0000 MHz in the LogicLoader™. Other clock speeds can be supported and modified in software for specific user applications, such as a specific serial baud rate.

The LH75401-10 Card Engine provides an external Bus clock, uP\_BUS\_CLK, on the 144-pin SO-DIMM connector at a frequency of 25 MHz. The uP\_BUS\_CLK is required for the wired LAN and the CPLD and may be used for other peripheral devices via the expansion connectors.

| LH75401 Microcontroller<br>Signal Name | LH75401-10/11 Card<br>Engine Net Name | Default Software Value in<br>LogicLoader™ |

|----------------------------------------|---------------------------------------|-------------------------------------------|

| HCLK                                   | N/A                                   | 51.6096 MHz/70.0000 MHz                   |

| N/A                                    | uP_BUS_CLK                            | 25.000 MHz                                |

**IMPORTANT NOTE:** The uP\_BUS\_CLK is not an output from the processor. The uP\_BUS\_CLK signal is created from a 25 MHz oscillator which drives the Wired LAN and CPLD timings.

### 2.3 Memory

#### 2.3.1 SRAM

The LH75401-10/11 Card Engine uses a 16-bit memory bus to interface to SRAM. The memory can be configured as 256 KB, 512 KB, 1 MB, or 2 MB to meet the user's memory requirements and cost constraints. The default memory configuration is a 512 KB configuration.

#### 2.3.2 Direct Memory Access (DMA)

The Sharp LH75401 microcontroller has an internal DMA controller with 4 DMA data streams; only one external DMA channel is available to the user. The standard LH75401-10 Card Engine uses external DMA Channel 0 to interface with the onboard audio CODEC - Texas Instruments TLV320DAC23. If an external DMA channel is required, please contact Logic Product Development.

#### 2.3.3 NOR Flash

The LH75401-10/11 Card Engine uses a 16-bit memory bus to interface to StrataFlash. The on board Card Engine memory is typically configured as 4 MBytes but can be configured as 4 or 8 MBytes to meet the user's flash requirements and cost constraints. A user should consult Logic when specifying flash size because it is one of the most expensive components in the LH75401-10/11 Card Engine.

A user can expand their non-volatile storage capability using the LH75401-10/11 Card Engine Application Kit as a design reference. Users can expand their non-volatile storage capability by external flash IC's, CompactFlash, or NAND Flash. See the LH75401-10 Application Kit for reference designs or contact Logic for other reference designs of peripheral interfaces.

#### 2.3.4 CompactFlash (memory-mapped mode only)

The LH75401 microcontroller does not have an on chip integrated CompactFlash controller. However, for applications requiring larger non-volatile storage, the LH75401-10/11 Card Engine provides the necessary signals using the CPLD for a CompactFlash card interface in memory-

mapped mode only. The Zoom™ Starter Kit reference design includes a CompactFlash connector for memory-mapped mode, but does not support the hot-swappable capability. See the LH75401-10/11 IO Controller Specification for further details.

Logic PN: 70000047

**IMPORTANT NOTE:** Additional hardware is required on the user's daughter board to provide hot-swapping capability.

**IMPORTANT NOTE:** The CPLD CompactFlash interface supports memory-mapped mode only. Designs requiring other CompactFlash modes should use an external controller or select a Card Engine with an integrated CompactFlash interface.

#### 2.4 10/100 Ethernet Controller

The LH75401-10/11 Card Engine uses the SMSC 91C111 10/100 Ethernet single chip solution. The Card Engine Ethernet interface provides an easy to use interface. The Card Engine provides six signals from the 91C111: ETHER\_TX(+), ETHER\_TX(-), ETHER\_RX(+), ETHER\_RX(-), ETHER\_NACT\_LED, and ETHER\_NLNK\_LED. The four analog PHY interface signals (ETHER\_TX(+), ETHER\_TX(-), ETHER\_RX(-), and ETHER\_RX(-)) require an external impedance matching circuit. Logic provides an example circuit schematics in the LH75401-10/11 Application Kit for reference.

**IMPORTANT NOTE:** Eneep signal on the SMSC 91C111 is connected to R15(np) (zero ohm resistor) that is not populated. Eneep signal has an internal weak pull up in the SMSC 91C111. If Eneep signal is tied low it will disable the serial EEPROM interface.

#### 2.5 Audio Codec

The LH75401-10/11 Card Engine uses the TI TLV320DAC23GQE high performance low cost stereo audio codec. Low power consumption and flexible power management allow selective control of the DAC functions on this component to optimize low power designs. The TLV320DAC23GQE audio codec has a single channel stereo input and single channel stereo output, but the LH75401-10/11 Card Engine does not support stereo input on its standard card engine.

Figure 2.2: Audio CODEC Block Diagram

IMPORTANT NOTE: Stereo In not supported in default LH75401-10/11 Card Engine

The LH75401-10/11 Card Engine supports a 10-bit stereo out. The audio codec uses a 5.6448 MHz crystal. The audio codec is software programmable via the SPI interface in the CPLD. See the CPLD Interface Specification for programming information. The audio codec provides software programmable sample rates, volume control, mute, and power management. See the TI Audio Codec TLV320DAC23 specification for programmable register settings and additional features and functionality.

Logic has interfaced other high performance audio codecs to the Card Engines. Contact Logic for assistance in selecting an appropriate audio codec for your application.

#### 2.6 Video Interface

Sharp's LH75401 microcontroller has a built in LCD controller supporting STN, TFT, HR-TFT and AD-TFT panels at VGA (640 x 480) Black and White, Grayscale, or 4 bpp VGA color or up to QVGA (320 x 240) Color. See the LH75401 Universal Microcontroller User's Guide for further information on the integrated LCD controller. The LCD controller signals from the LH75401-10/11 are located on one of the Card Engine's 80-pin expansion connectors. Logic has written drivers for numerous panels of different types and sizes. Please contact Logic Product Development before selecting a panel for your application.

**IMPORTANT NOTE:** Using the internal graphics controller will affect processor performance. Selecting display resolutions and color bits per pixel will vary processor bus load.

#### 2.7 Serial Interface

The LH75401-10/11 Card Engine comes with the following serial channels: UARTA, UARTB, UARTC, and SPI. If additional serial channels are required, please contact Logic for reference designs.

#### 2.7.1 **UARTA**

UARTA has been configured to be the LH75401 main serial port. It has similar functionality to the industry standard 82510. This SCIF interface is a high-speed serial interface with a FIFO (asynchronous or synchronous) and is capable of sending and receiving serial data simultaneously. The signals from the Card Engine are TTL level signals not RS232 level. The user must provide an external RS232 transceiver for RS232 applications. Logic has provided an example reference design with the Zoom™ Starter Kit. When choosing an RS232 transceiver, the user should keep in mind cost, availability, ESD protection, and data rates.

UARTA is available off the 144-pin SO-DIMM connector and is capable of supporting baud rates up to 3.225M bits/sec (given system clock as 51.6096MHz or 70.0000MHz). Please see the LH75401 Universal Microcontroller User's Guide for further information.

#### 2.7.2 **UARTB**

Serial Port UARTB has dual functionality, its primary function is as an asynchronous 16C550 compatible UART. This SCIF interface is also a high-speed serial interface with a 1-16 byte programmable FIFO (asynchronous or synchronous) and is capable of sending and receiving serial data simultaneously. This port can also be programmed to utilize the on-chip DMA to reduce processor bandwidth required to service UART activities. The signals from the Card Engine are TTL level signals not RS232 level. The user is responsible for providing an external RS232 transceiver for RS232 applications. UARTB's baud rate can also be set to all common serial baud rates from 110bps to 921.6K bits/sec.

Serial Port UARTB is multiplexed with IRQ lines D and E. If you use UARTB, you can not use IRQ lines D and E; conversely, if you use IRQ lines D and/or E, you can not use UARTB.

#### 2.7.3 **UARTC**

Serial Port UARTC also has dual functionality, its primary function is as an asynchronous 16C550 compatible UART. This SCIF interface is also a high-speed serial interface with a 1-16 byte programmable FIFO (asynchronous or synchronous) and is capable of sending and receiving serial data simultaneously. This port can also be programmed to utilize the on-chip DMA to reduce processor bandwidth required to service UART activities. The signals from the Card Engine are TTL level signals not RS232 level. The user is responsible for providing an external RS232 transceiver for RS232 applications. UARTC's baud rate can also be set to all common serial baud rates from 110bps to 921.6K bits/sec.

Serial Port UARTC is multiplexed to allow CAN 2.0b functionality. The CAN 2.0b controller is an AMBA-compliant peripheral that connects as a slave to the APB.

#### 2.7.4 SPI

The SPI interface on the LH75401 is a SSP (synchronous serial port) used to facilitate synchronous serial communications with slave peripheral devices. This serial port is a Master-only device, with programmable clock bit-rate and prescale factors. It supports three data frame formats:

- Texas Instruments' SSI

- Motorola SPI<sup>TM</sup>

- National Semiconductor Microwire<sup>TM</sup>

The SPI interface signals are available off the 144-pin SO-DIMM connector. Please see the LH75401 Universal Microcontroller User's Guide for further information.

#### 2.8 CAN

The LH75401 processor has an integrated CAN controller. The CAN communications are performed serially at a maximum frequency of 1Mbit/s with a 64byte receive FIFO. The controller has full compliance with the 2.0A and 2.0B Bosch specifications. The CAN pins are multiplexed with the UARTC on the LH75401-10/11 Card Engine. An external CAN transceiver is required for interfacing with the CAN controller on the LH75401-10/11 Card Engine, please contact Logic Product Development for recommendations concerning interfacing.

Figure 2.3 CAN Controller Block Diagram

#### 2.9 Touch Interface

Touch interface is supported on the LH75401-10/11 Card Engine for standard 4-wire resistive touch panels. The LH75401 processor has 8 Analog-to-Digital Converter (ADC) channels, of which 4 are used for the analog touch interface (AN0-AN3).

The analog touch interface signals on the external connectors are: TOUCH\_TOP, TOUCH\_BOTTOM, TOUCH\_RIGHT and TOUCH\_LEFT.

**IMPORTANT NOTE:** The net names reflect the side of the touch screen that they should be attached to and do not necessarily mean X or Y axis, as the terms "X" and "Y" can be interpreted in different ways.

#### 2.10 General Purpose Analog & Digital I/O

Logic designed the LH75401-10/11 Card Engine to be flexible and provided multiple options for analog and digital GPIO. There are numerous digital GPIO on the Card Engine that interface to the LH75401, and the Altera CPLD. Some of these GPIO are interrupt capable while other signals are input or output only. Please see the Pin Descriptions section of this data sheet.

The LH75401 microcontroller has 4 Analog-to-Digital conversion channels that are available to the user through the expansion bus connectors (the remaining 4 channels are used for the touch screen interface as previously mentioned). If certain peripherals are not used, such as the LCD Controller, Chip Selects, IRQs, UARTs, or SPI port multiple GPIO pins become available. Please see the table in section 5 entitled "Multiplexed Signal Trade-Offs." This table lists the available GPIO trade-offs that are available when certain peripheral functions are not used.

#### 2.11 CPLD

Please see the LH75401-10/11 IO Controller Specification for CPLD information.

#### 2.12 Serial EEPROM Interface

Logic designed the LH75401-10/11 Card Engine to have a low cost 1 kbit serial EEPROM for non-volatile data storage. The serial EEPROM is connected to the LH75401 microcontroller via the CPLD through a SPI interface. See Figure 5 below. Please see the LH75401-10/11 IO Controller Specification for CPLD information.

Figure 2.4: Serial EEPROM Block Diagram

#### 2.13 Expansion Options

The LH75401-10/11 Card Engine was designed for expansion and provides all the necessary control signals and bus signals to expand the user's design. Many of these signals are buffered and brought out to the 144-pin SO-DIMM connector and two 80-pin expansion connectors. See the LH75401-10/11 Card Engine schematics for more detail. A user can expand the Card Engine's functionality such as PCI, Compact Flash, PCMCIA, ISA devices, PCI devices, etc.. Logic has expanded the Card Engine to other audio codecs, Ethernet IC's, UARTs, Coprocessors, etc.. Please contact Logic for potential reference designs before selecting your peripherals.

### 3 System Integration

#### 3.1 Configuration

The LH75401-10/11 Card Engine was designed to be configurable to meet user's applications and budget needs. The Card Engine supports a variety of embedded operating systems and comes in the following hardware configurations:

- Flexible memory footprint: 256k bytes, 512k bytes, 1 MByte, 2MByte SRAM

- Flexible FLASH footprint: 4 or 8 MBytes StrataFlash

- Optional SMSC 91C111 10/100 Ethernet Controller

- Optional TI TLV320DAC23GQE Audio Codec

Please contact Logic Product Development for additional hardware configurations to meet your application.

#### 3.2 Resets

#### 3.2.1 Master Reset (Hard Reset)

All hardware peripherals should connect their hardware-reset pin to the MSTR\_nRST signal on the SODIMM connector. All internal card engine peripheral hardware reset pins are connected to either the MSTR\_nRST net or to the RESET\_HIGH net as shown in the figure below. The MSTR\_nRST signal is an open-drain output, enabling the user to assert the MSTR\_nRST signal externally to the card engine. Logic suggests that custom designs implemented with the LH75401-10/11 Card Engine use the MSTR\_nRST signal as the "pin hole" reset used in commercial embedded systems.

Figure 3.1: Reset Circuit

The MSTR\_nRST signal is an active low output of the reset chip, located on the card engine. The RESET\_HIGH signal is an active high output of the reset circuit and is not provided as part of the card engine connector interface.

**IMPORTANT NOTE:** The custom design should guard the assertion of the reset lines during a low power state so the microprocessor cannot be reset and powered on in a low or bad power condition (will cause data corruption and possible temporary system lockup). See section entitled "Power Management" for further details.

There are three conditions that will generate a low on the output reset pin of the reset chip (the MSTR\_nRST signal): power-on condition, a low pulse on the MSTR\_nRST signal, and the power fail comparator input (PFI pin) falling below the internal comparator threshold.

#### Power On:

At power on, MSTR\_nRST signal is asserted low when the supply voltage (VDD) of the reset chip is between 0.4V and 2.941V. Once the 3.3V\_uP\_SRAM supply becomes higher than 2.941V, an internal timer will delay the rising edge of MSTR\_nRST from 65 to 195 mS (130 mS typical).

#### Low Pulse on MSTR\_nRST Signal:

A low pulse on the MSTR\_nRST signal of the reset chip, asserted by an external source (custom design or application board) will bring MSTR\_nRST low until the assertion source is de-asserted. There is no delay beyond the de-assertion of the external MSTR\_nRST signal source, so the custom design must ensure that the assertion time is sufficient for all related peripherals.

Logic also suggests analog or digital de-bouncing of an external assertion source of the MSTR\_nRST signal.

#### Power Fail:

If the power fail comparator input pin (PFI pin) falls below the internal comparator threshold of 0.551V, it will create a low pulse on the MR input pin of the reset chip. The low assertion of the MR pin will assert the MSTR\_nRST signal and will hold it low after the MR pin is deasserted (PFI is above the comparator level – power is restored) for 65 to 195 mS (130 mS typical).

Please see the TI TPS3103 data sheet at <a href="http://www.ti.com">http://www.ti.com</a> for additional details on reset timing and thresholds.

#### 3.2.2 Soft Reset

Logic has created a soft reset signal named uP\_SW\_nRESET that can be used to reset the LH75401 microprocessor's internal registers without affecting the peripherals on the rest of the board and without losing data stored in SRAM or other volatile storage. The uP\_SW\_nRESET signal is an input to LH75401-10/11 Card Engine's CPLD.

#### 3.3 Interrupts

The LH75401 responds to ARM exceptions and vectored interrupts generated by the onboard-vectored interrupt controller (VIC). The LH75401 accepts inputs from 32 interrupt sources--23 are from internal sources, and 7 are from external sources and 2 can be controlled by software. All interrupts are routed to the VIC where priorities are determined by hardware and the appropriate interrupt signal is dispatched to the ARM7 exception-handling hardware. Lower numbered interrupts have higher priority than higher-numbered interrupts. Each external interrupt has rising edge, falling edge, HIGH level, or LOW-level trigger options. The LH75401-10/11 Card Engine interrupts are set to trigger on a LOW level by default. The LH75401-10/11 Card Engine provides 5 available interrupt sources. Each of the interrupts can be separately setup as FIQs via software. Refer to Sharp's LH75401 Universal Microcontroller User's Guide for further information.

**IMPORTANT NOTE:** See LH75401-10/11 IO Controller Specification for detailed information on the use of the CPLD interrupt (signal uP\_CPLD\_IRQ).

#### 3.4 JTAG Debugger Interface

There are many different third party JTAG debuggers available for Sharp ARM microcontrollers. The JTAG connection enables a user to recover a board that has corrupted flash memory and to debug real time applications. The following signals make up the JTAG interface to the LH75401, for connection to a JTAG emulator: uP\_TRST, uP\_TDI, uP\_TMS, uP\_TCK, uP\_TDO, and uP\_RTCK. These signals should interface directly to a 20-pin 0.1" through-hole connector as demonstrated in the Sharp LH75401 Universal Microcontroller User's Guide, or as shown on reference schematics.

**IMPORTANT NOTE:** When laying the 20 pin connector out, realize it may not be numbered as a standard 20 pin 0.1" IDC through-hole connector. See LH75401-10/11 Card Engine Application Kit reference design for further details. Different IC manufacturers define the 14 pin IDC connector pin-out differently.

### 3.5 Power Management

#### 3.5.1 System Power Supplies

The LH75401-10/11 Card Engine was designed to have the following five power areas, 3.3V\_uP\_SRAM, 3.3V, 3.3VA, 3.3V\_WRLAN and VCORE for a flexible hardware design. All power areas are inputs to the card engine with the exception of 3.3V\_WRLAN, which is an output from the card engine.

#### 3.5.1.1 3.3V\_uP\_SRAM

The 3.3V\_uP\_SRAM input pins are designed to be connected to a 3.3V power supply with optional backup battery. If the design is required to maintain SRAM contents in a critical power situation (low battery, loss of power), the 3.3V\_uP\_SRAM supply should be maintained above the minimum level at all costs (see Electrical Specifications section). Logic suggests using STANDBY mode with its software BSPs to prepare the system for the critical power condition. In order to do this, STANDBY mode puts the processor into the standby state. Please see the description of STANDBY mode later in this section.

#### 3.5.1.2 3.3V

The power nets connected to the 3.3V power plane power the majority of the peripheral's digital supply pins on the LH75401-10/11 Card Engine. This supply must stay within the acceptable levels as specified in the Electrical Specification section of this manual, unless powering down the board or under critical power conditions.

Under critical power conditions, Logic suggests first notifying the system through the assertion of a STANDBY sequence and then powering this supply off.

#### 3.5.1.3 3.3VA

The power nets connected to the 3.3VA power plane power all analog power supply pins of both the LH75401 microprocessor and applicable peripherals on the LH75401-10/11 Card Engine. This supply must stay within the acceptable levels as specified in the Electrical Specification section of this manual, unless powering down the board or under critical power conditions.

Under critical power conditions, Logic suggests first notifying the system through the assertion of a STANDBY sequence and then powering this supply off.

#### 3.5.1.4 3.3V\_WRLAN

This "power" supply net is an output from the card engine. It is controlled through a registered bit in the on-board CPLD. See the "LH75401-10/11 IO Controller Specification" for specific details on this control bit. Logic's software BSPs assert this signal as appropriate. This is done because the software power management in the 91C111 does not put the part in a low enough power state for many applications.

The custom application board should use this power supply output pin to supply the Ethernet impedance matching resistors with power. They should not be connected to 3.3V directly or the entire Ethernet controller circuit on the card engine will try to power itself through the impedance matching resistors. Please see Logic's schematics for the Zoom™ Starter Kit or other reference designs for details.

**IMPORTANT NOTE:** The purpose of the 3.3V\_WRLAN power plane on the card engine is to power the 91c111 separately and give the ability to shut it off completely but independently. The 3.3V\_WRLAN output from the card engine is required to completely isolate the LAN circuit such that it is not back powered through the impedance matching resistors.

#### 3.5.1.5 VCORE

The VCORE input pins are designed to be connected to a 1.8V power supply with optional backup battery. If the design is required to maintain SRAM contents in a critical power situation (low battery, loss of power), the VCORE supply should be maintained above the minimum level at all costs (see Electrical Specifications section). Logic suggests using STANDBY mode with its software BSPs to prepare the system for the critical power condition. In order to do this, STANDBY mode puts the processor into the standby state. Please see the description of STANDBY mode later in this section.

| Logic Net<br>Name | Required Input VDC | Notes                                                                                                                                                                                                                                                                     |

|-------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3V_uP_<br>SDRAM | 3.3 VDC            | Connects to the Processor's 3.3-volt pins and the SDRAM. This net can be used for battery powered or bridge battery applications that require the processor and the SDRAM to refresh.                                                                                     |

| 3.3V              | 3.3 VDC            | Connects to the digital peripherals on the Card Engine.                                                                                                                                                                                                                   |

| 3.3VA             | 3.3 VDC            | Connects to the Audio Codec on the Card Engine to provide a clean analog plane. The user may choose not to provide a clean analog plane depending on their performance requirements.                                                                                      |

| 3.3V_WRLAN        | NA                 | The 3.3V_WRLAN is located on the Card Engine only and provides power to the SMSC 911C111 processor. The power to the 3.3V_WRLAN area is controlled by the signal WRLAN_ENABLE from the CPLD. See the CPLD IO Controller Spec. for information on controlling the WRLAN_E. |

| VCORE             | See note           | Connects to the processor core voltage. See specific processor for VCORE voltage. Many processors require different VCORE voltages for different operating frequencies, temperature, etc.                                                                                 |

Figure 3.2: Power Plane Diagram

**IMPORTANT NOTE:** The purpose of the PMOS FET to control the power to the SMSC 91C111 is because the software power management in the 91C111 is not suitable for many applications.

**IMPORTANT NOTE**: The LH75401-10/11 Card Engine hardware architecture was designed for low power battery operated applications. However, the Altera CPLD on the LH75401-10/11 Card Engine is not an ideal part for low power battery operated designs. This specific component was chosen for cost. If one is using the LH75401-10/11 Card Engine as a reference design, one can consider other programmable logic devices that are optimized for power, not cost.

#### 3.5.2 Peripherals

Most peripherals provide software programmable power states. The audio codec and touch controller have programmable power states. Please see the appropriate data sheet for more information and the CPLD Interface Specification for details. The SMSC 91C111 controller has

software programmable power states but may not be sufficient for some applications. Logic has provided hardware to cut power to the 91C111 IC.

Logic PN: 70000047

#### 3.5.3 System Power Management

Good power management design happens in the hardware and software of any system. Typically, the power management design of any embedded system can be one of the most complicated parts and has a dramatic effect on the overall product cost, performance, usability, and customer satisfaction. Many factors effect good power management design in the hardware including: power supply selection (efficiency), clocking design, IC and component selection, etc. The LH75401-10/11 Card Engine electronics were designed to provide maximum flexibility to the software and system integrator.

There are many different software configurations which drastically effect the power consumption of the LH75401-10/11 Card Engine including: microprocessor core clock frequency, microprocessor bus clock frequency, microprocessor peripheral clocks, microprocessor bus utilization, microprocessor power management states (normal, sleep, standby, module-standby), peripheral power states and modes, product user scenarios, interrupt handling, display settings (resolution, backlight, refresh, bits per pixel, etc..) These settings are typically initialized in the startup software routines and may be later modified in the operating system and application software. These items are covered in the appropriate documents such as the Bootloader User's Manual or appropriate BSP manual.

#### 3.5.4 Microcontroller

The LH75401-10/11 Card Engine power management's scheme was designed to be easy to use. There are five power management states provided in the LH75401 microcontroller: ACTIVE, STANDBY, SLEEP, STOP1, and STOP2. Sharp's LH75401 provides complex power management features. Please see the LH75401 Universal Microcontroller User's Guide for more details.

**IMPORTANT NOTE:** The BSP's available from Logic for the different operating systems supported on the LH75401 may not support all five of the power management states. Please see the appropriate BSP documentation for power management modes for more detail.

#### 3.5.4.1 Active Mode

The LH75401-10/11 Card Engine normal operating state is ACTIVE. The LH75401 system on a chip enters this mode on reset and returns to this mode when any interrupt is received, if operating in any other power mode. The LH75401 cannot transition directly between the other power modes; it will always return to active mode before entering any other power mode.

#### 3.5.4.2 Standby Mode

The Standby mode halts the clocks to the CPU while leaving the remainder of the chip active. The LH75401 transitions from the Standby mode to the Active mode when an interrupt is received.

#### 3.5.4.3 Sleep Mode

The Sleep mode halts all system clocks. Only the PLL and the internal oscillators remain active. If the 32.768 kHz internal oscillator is in use, it will also remain active. The LH75401 transitions from the Sleep mode to the Active mode when an interrupt is received.

When transitioning from the Active mode to the Sleep mode, the LH75401 Power Management system automatically performs the following sequence:

- Acquires control of the AHB, to ensure that all transactions are completed.

- Ensures that all SRAM devices are placed in the self-refresh mode of operation.

- Halts all output clocks that are driven by HCLK, HCLK\_CPU, and PCLK

- Waits for IRQ or FIQ to be asserted (which will return the LH75401 to the Active mode).

When an IRQ or FIQ occurs, the LH75401 returns to the Active mode, restarts the output clocks, resumes SDRAM refresh and then cedes control of the AHB.

#### 3.5.4.4 Stop1 Mode

The Stop1 mode halts all system clocks and disables the PLL but keeps the internal oscillators active. If the 32.768 kHz internal oscillator is in use, it will remain active. The LH75401 transitions from the Stop1 mode to the Active mode when an interrupt is received. When transitioning from the Active mode to the Stop1 mode, the LH75401 Power Management system automatically performs the following sequence:

- Acquire control of the AHB, to ensure that all transactions are completed.

- Ensure that all SRAM devices are placed in the self-refresh mode of operation.

- Wait for IRQ or FIQ to be asserted (which will return the LH75401 to the Active mode).

When an IRQ or FIQ occurs, the LH75401 returns to the Active mode, restarts the output clocks (which may require a delay for the PLL to reacquire lock, if the PLL is in use), then returns control of the AHB.

#### 3.5.4.5 Stop2 Mode

The Stop2 mode halts all system clocks and disables both the PLL and the internal oscillators that feed it. If the 32.768 kHz internal oscillator is in use, it will remain active. The LH75401 transitions from the Stop2 mode to the Active mode when an interrupt is received.

When transitioning from the Active mode to the Stop2 mode, the LH75401 Power Management system automatically performs the following sequence:

- Acquire control of the AHB, to ensure that all transactions are completed.

- Ensure that all SRAM devices are placed in the self-refresh mode of operation.

- Halts all clocks, disable the PLL, disable the 14.7456 MHz/20.0000 MHz oscillator.

- Wait for IRQ or FIQ to be asserted (which will return the LH75401 to the Active mode).

When an IRQ or FIQ occurs, the LH75401 returns to the Active mode, restarts the output clocks (which may require a delay for the PLL to reacquire lock, if the PLL is in use), then returns control of the AHB.

#### 3.6 ESD Considerations

The LH75401-10 Card Engine was designed to interface to a customer's peripheral board. The Card Engine was designed to be low cost and adaptable to many different applications. The LH75401-10/11 Card Engine does not provide any ESD protection circuitry on the card and must be provided by the product it is used in. Logic has extensive experience in designing products with ESD requirements. Please contact Logic if you need any assistance in ESD design considerations.

## 4 Memory & I/O Mapping

### 4.1 SRAM Memory Map

Note, this is the standard boot memory map for the LH75401 processor. No re-mapping has been performed.

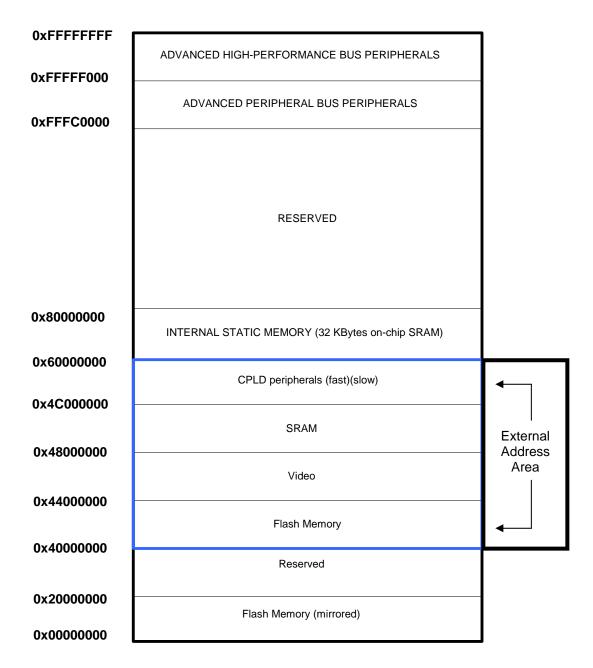

Figure 4.1: LH75401 Card Engine General Memory Map

### 4.2 External Static Memory Map

#### 4.2.1 Card Engine Static Memory Map Description

The table below indicates what each bank of external static memory is being used for on the card engine.

| Chip Select | Bank | Start Address | Memory Description                          |

|-------------|------|---------------|---------------------------------------------|

| nCS3        | 3    | 0x4C00 0000   | CPLD peripherals (fast)/(slow) <sup>2</sup> |

| nCS2        | 2    | 0x4800 0000   | SRAM                                        |

| nCS1        | 1    | 0x4400 0000   | Video <sup>3</sup>                          |

| nCS0        | 0    | 0x4000 0000   | Boot Device (FLASH or EEPROM <sup>3</sup> ) |

#### Notes:

- 2. CPLD peripherals are those components that get a decoded chip select from the CPLD. (i.e. CPLD memory mapped registers, onboard SMSC 91C111 Ethernet controller, etc... Please see the LH75401-10/11 IO Controller Specification document for details.)

- 3. Components planned for future applications.

### 5 Pin Descriptions & Functions

**IMPORTANT NOTE:** The following pin descriptions and states are described after the initialization of the LogicLoader<sup>™</sup> (bootloader). Many of the signals defined in the tables below can be configured as input or outputs, active low or active high, and have different functions. It is critical to review all signals in the final design (both electrical and software) to verify the necessary configuration (external pull ups/pull downs).

In addition, keep in mind that the following mode line numbers on the card engine do not necessarily line up with the mode line numbers on the processor.

### 5.1 J1C Connector SO-DIMM 144-Pin Descriptions

| Pin# | Signal Name    | I/O              | Description                                                                                                                                                                                                                                                                                                                                                                        |

|------|----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | ETHER_RX(-)    | I                | This input pair receives 10/100 MB/s Manchester encoded data from the 10/100 BASE-T receive lines. Route as differential pair with ETHER_RX(+).                                                                                                                                                                                                                                    |

| 2    | MSTR_nRST      | I/O <sup>1</sup> | Active Low. This signal initiates a hard reset (power on) – external memory contents are lost during reset. Every peripheral on the card engine with a reset line is reset with the assertion of this signal. Refer to LH75401 processor datasheet for register states during or after power on reset. This signal has a 10k pull up on the card engine.                           |

| 3    | ETHER_RX(+)    | ı                | This input pair receives 10/100 MB/s Manchester encoded data from the 10/100 BASE-T receive lines. Route as differential pair with ETHER_RX(-).                                                                                                                                                                                                                                    |

| 4    | uP_SW_nRESET   | l <sup>1</sup>   | Active Low. This signal initiates a soft reset (manual reset) – external memory contents are retained during reset. This pin is connected to the CPLD, please see LH75401-10/11 IO Controller Specification for detailed information on the use of the CPLD based reset. This signal has a 10k pull up on the card engine.                                                         |

| 5    | ETHER_TX(-)    | 0                | This output pair drives 10/100 Mb/s Manchester-encoded data to the 10/100 BASE-T transmit lines. Route as differential pair with ETHER_TX(+).                                                                                                                                                                                                                                      |

| 6    | FAST_nMCS      | 0                | Active Low. Buffered chip select for area 4 of LH75401-10/11 memory. This is the "fast" peripheral chip select area. This is set to a 16 bit wide area and should not be changed. See memory map for details.                                                                                                                                                                      |

| 7    | ETHER_TX(+)    | 0                | This output pair drives 10/100 Mb/s Manchester-encoded data to the 10/100 BASE-T transmit lines. Route as differential pair with ETHER_TX(-).                                                                                                                                                                                                                                      |

| 8    |                | NC               | No internal connection (not implemented on the LH75401-10/11)                                                                                                                                                                                                                                                                                                                      |

| 9    | DGND           | ı                | Digital Ground (0V)                                                                                                                                                                                                                                                                                                                                                                |

| 10   | VIDEO_nMCS     | 0                | Active Low. Buffered chip select for area 2 of LH75401-10/11 memory. This is the "video" chip select area. This chip select is also capable of controlling additional external SRAM. This is set to a 16 bit wide area and can be changed based on the user's needs. See memory map for details.                                                                                   |

| 11   | ETHER_nACT_LED | 0                | Active Low open drain output. 24mA sink. This output indicates transmission or reception of frames or detection of a collision. This signal may be connected directly to an external LED.                                                                                                                                                                                          |

| 12   | BOOT_nMCS      | 0                | Active Low. This signal is the buffered chip select for boot ROM and is connected to area 0 of LH75401-10/11 memory when uP_MODE3 is low. When uP_MODE3 is high, this signal is activated at a specific memory mapped address in the slow chip select area (16 bit wide area 2). The memory width for area 0 is selectable with uP_MODE0 and uP_MODE1. See memory map for details. |

| 13   | ETHER_nLNK_LED | 0                | Active Low open drain output. 24mA sink. This output indicates valid link pulses. May be connected directly to an external LED.                                                                                                                                                                                                                                                    |

| 14   | nIOWR          | 0                | Active Low. This signal is driven by the ISA bus master or DMA controller to signal valid write data on the data bus. A peripheral may use this signal to latch the data in. See the LH75401-10/11 IO Controller Specification for further details.                                                                                                                                |

| Pin# | Signal Name | I/O            | Description                                                                                                                                                                                                                                                                                                                                                    |

|------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | nSTANDBY    | I <sup>1</sup> | Active Low. CPU power mode signal. This signal is registered in the CPLD. Please reference the LH75401-10/11 IO Controler Specification for implementation. This signal has a 10k pull up on the card engine.                                                                                                                                                  |

| 16   | nIORD       | 0              | Active Low. This signal is driven by the ISA bus master or DMA controller to request an I/O resource to drive data onto the data bus during the cycle. See the LH75401-10/11 IO Controller Specification for further details.                                                                                                                                  |

| 17   | DGND        | I              | Digital Ground (0V)                                                                                                                                                                                                                                                                                                                                            |

| 18   | 3.3V_WRLAN  | 0              | Power Supply (3.3V) from the 10/100 wired LAN circuit. This pin is used to power the impedance matching resistor network on the Ethernet's TX and RX lines. It should not be connected to anything else. It may be shut down when appropriate (software controlled to cut power off to the wired LAN circuit).                                                 |

| 19   | 3.3V        | I              | Power Supply (3.3V)                                                                                                                                                                                                                                                                                                                                            |

| 20   | BALE        | 0              | Active High. This signal is driven high to indicate when the MA<19:0> signal lines are valid. See the LH75401-10/11 IO Controller Specification for further details.                                                                                                                                                                                           |

| 21   |             | NC             | No internal connection (not implemented on the LH75401-10/11)                                                                                                                                                                                                                                                                                                  |

| 22   | nCHRDY      | I <sup>1</sup> | Active Low. The I/O channel ready signal line allows the resources to indicate to the ISA bus master that additional cycle time is required. Peripherals using this signal must make their outputs open drain, as it is a shared bus. See the LH75401-10/11 IO Controller Specification for further details. This signal has a 10k pull up on the card engine. |

| 23   |             | NC             | No internal connection (not implemented on the LH75401-10/11)                                                                                                                                                                                                                                                                                                  |

| 24   | uP_TEST1    | l <sup>1</sup> | This is connected to Test Mode Pin 1 on the LH75401 processor. Please see the section on Operating Modes in the LH75401 technical datasheet for detailed operation. This signal has a 10k pull up on the card engine.                                                                                                                                          |

| 25   | uP_IRQC     | l <sup>1</sup> | Active Low. Dedicated hardware interrupt on LH7A400-10. May also be configured as a general-purpose input only pin. This signal is pulled up to 3.3V_uP_SRAM through a 10K resistor.                                                                                                                                                                           |

| 26   | uP_TEST2    | 1              | This is connected to Test Mode Pin 2 on the LH75401 processor. Please see the section on Operating Modes in the LH75401 technical datasheet for detailed operation. This signal has a 10k pull up on the card engine.                                                                                                                                          |

| 27   | uP_IRQB     | I <sup>1</sup> | Active Low. Dedicated hardware interrupt on LH7A400-10. May also be configured as a general-purpose input only pin. This signal is pulled up to 3.3V_uP_SRAM through a 10K resistor.                                                                                                                                                                           |

| 28   | uP_TRST     | l <sup>1</sup> | This signal is pulled up to 3.3V_uP_SRAM through a 10K resistor.                                                                                                                                                                                                                                                                                               |

| 29   | uP_IRQA     | I <sup>1</sup> | Active Low. Dedicated hardware interrupt on LH7A400-10. May also be configured as a general-purpose input only pin. This signal is pulled up to 3.3V_uP_SRAM through a 10K resistor.                                                                                                                                                                           |

| 30   | uP_TMS      | I <sup>1</sup> | JTAG Test Mode Select Input. May leave unconnected if not using the JTAG port. This signal has a 10k pull up on the card engine.                                                                                                                                                                                                                               |

| 31   |             | NC             | No internal connection (not implemented on the LH75401-10/11)                                                                                                                                                                                                                                                                                                  |

| 32   | uP_TDO      | 0              | JTAG Test Data Serial Output. Leave unconnected when JTAG port is not in use. This signal has a 10k pull up on the card engine.                                                                                                                                                                                                                                |

| 33   |             | NC             | No internal connection (not implemented on the LH75401-10/11)                                                                                                                                                                                                                                                                                                  |

| 34   | uP_TDI      | l <sup>1</sup> | JTAG Test Serial Data Input. May leave unconnected if not using the JTAG port. This signal has a 10k pull up on the card engine.                                                                                                                                                                                                                               |

| 35   |             | NC             | No internal connection (not implemented on the LH75401-10/11)                                                                                                                                                                                                                                                                                                  |

| 36   | uP_TCK      | l <sup>1</sup> | JTAG Test Clock Input. May leave unconnected if not using the JTAG port. This signal has a 10k pull up on the card engine.                                                                                                                                                                                                                                     |

| 37   | uP nWAIT    |                | Active low. The WAIT signal requests the current bus cycle be extended until this signal is de-asserted. This signal will completely halt processor operations until it is de-asserted and the bus cycle is ended. Peripherals using this signal must make their outputs open drain, as it is a shared bus.                                                    |

| 3/   | uP_nWAIT    | I              | This signal has a 10K pull up resistor to 3.3V_uP_SRAM on the card engine.                                                                                                                                                                                                                                                                                     |

| Pin # | Signal Name   | I/O            | Description                                                                                                                                                |  |

|-------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       | org           |                | Boot select signal (0 = external boot device, 1 = onboard flash). This                                                                                     |  |

|       |               |                | defaults to high (onboard flash) if left unconnected (pulled to                                                                                            |  |

| 38    | uP_MODE3      | I <sup>1</sup> | 3.3V_uP_SRAM through a 10K pullup resistor).                                                                                                               |  |

| 39    |               | NC             | No internal connection (not implemented on the LH75401-10/11)                                                                                              |  |

|       |               |                | The LH75401 processor only supports Little Endian memory operations. On                                                                                    |  |

|       |               |                | development kits by Logic Product Development, the generic use of this pin is an Endian setting (0 = big endian, 1 = little endian). This defaults to high |  |

|       |               |                | (little endian) if left unconnected (pulled to 3.3V_uP_SRAM through a 10K                                                                                  |  |

| 40    | uP_MODE2      | I <sup>1</sup> | pullup resistor).                                                                                                                                          |  |

| 41    |               | NC             | No internal connection (not implemented on the LH75401-10/11                                                                                               |  |

|       |               |                | This signal is registered in the CPLD. The LH75401 can only boot from 8 bit                                                                                |  |

| 42    | uP_MODE1      | I <sup>1</sup> | and 16 bit sources so uP_MODE1 is not required for determining external boot widths. This signal has a 10k pull up on the card engine.                     |  |

| 44    | uP_UARTA_TX - | '              | SCIF port (UARTA) transmit data output. Internally pulled up on the                                                                                        |  |

| 43    | PE1           | 0              | LH75401 processor.                                                                                                                                         |  |

|       |               |                | Bus width setting. $uP\_MODE0 - 0 = 8$ bit, $1 = 16$ bit. This signal is read                                                                              |  |

|       |               |                | immediately after power on reset and determines the boot width of area 0.                                                                                  |  |

|       |               |                | This changes BOOT_nCS bus size between 8 and 16 bits. This defaults to high if left unconnected (pulled to 3.3V_uP_SRAM through a 10K pullup               |  |

|       |               |                | resistor). The default state boots from the 16 bit flash chip on the card                                                                                  |  |

| 44    | uP_MODE0      | I <sup>1</sup> | engine.                                                                                                                                                    |  |

|       | uP_UARTA_RX - |                | SCIF port (UARTA) receive data input. Internally pulled up on the LH75401                                                                                  |  |

| 45    | PE2           |                | processor.                                                                                                                                                 |  |

| 46    |               | NC             | No internal connection (not implemented on the LH75401-10/11)                                                                                              |  |

| 47    |               | NC             | No internal connection (not implemented on the LH75401-10/11)                                                                                              |  |