#### **REVISION HISTORY**

| REV | EDITOR                         | REVISION DESCRIPTION                                                                                                                                             | LoLo Ver. | APPROVAL | DATE       |

|-----|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|------------|

| Α   | Bruce Rovner                   | Release                                                                                                                                                          | -         | B.R.     | 7/24/03    |

| В   | James Wicks                    | Figure 1.1 Revision                                                                                                                                              | •         | B.R.     | 10/17/2003 |

| С   | Chris Rempel,<br>Bruce Rovner  | Updated for LogicLoader Version 1.4 Release                                                                                                                      | 1.4       | B.R.     | 3/31/04    |

| D   | Aaron Stewart                  | Added Supported Options in LogicLoader                                                                                                                           | 1.4.4     | M.E.     | 12/3/04    |

| E   | Aaron Stewart,<br>Bruce Rovner | Update for LogicLoader 2.03 release. Updated Section 1 diagrams for exec and execution format. Updated supported options table for hardware support description. | 2.0.4     | H.R.     | 10/14/05   |

This file contains source code, ideas, techniques, and information (the Information) which are Proprietary and Confidential Information of Logic Product Development, Inc. This information may not be used by or disclosed to any third party except under written license, and shall be subject to the limitations prescribed under license.

No warranties of any nature are extended by this document. Any product and related material disclosed herein are only furnished pursuant and subject to the terms and conditions of a duly executed license or agreement to purchase or lease equipments. The only warranties made by Logic Product Development, if any, with respect to the products described in this document are set forth in such license or agreement. Logic Product Development cannot accept any financial or other responsibility that may be the result of your use of the information in this document or software material, including direct, indirect, special or consequential damages.

Logic Product Development may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering the subject matter in this document. Except as expressly provided in any written agreement from Logic Product Development, the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions.

© Copyright 2005, Logic Product Development, Inc. All Rights Reserved.

# **Table of Contents**

| 1 LH7A400-10 Memory Map Diagrams                            |   |

|-------------------------------------------------------------|---|

| 1.1 SDRAM Configuration                                     |   |

| 1.2 MMU Remap: Physical Memory to Logical Memory            |   |

| 1.3 Physical Hardware Memory Map                            |   |

| 1.4 LogicLoader and the Configuration Block in Flash Memory |   |

| 1.5 LogicLoader's Location in RAM                           |   |

| 2 LH7A400-10 LogicLoader Functionality                      | 8 |

| 2.1 Supported Hardware Peripherals                          | 8 |

| 3 Disclaimer                                                |   |

# 1 LH7A400-10 Memory Map Diagrams

## 1.1 SDRAM Configuration

The LH7A400-10 Card Engine is designed to accommodate SDRAM of different sizes. Under LogicLoader's default configuration, all memory installed is accessible, however on 64MB card engines the SROMLL bit is set to make two separate 32MB physical chunks. The MMU is then configured to make the two 32MB chunks appear as a single 64MB virtual chunk.

For further documentation: please refer to the Sharp LH7A400 User Guide for more information on the SDRAM controller. Please refer to the ARM 922T Technical Reference Manual for more information on the MMU.

### 1.2 MMU Remap: Physical Memory to Logical Memory

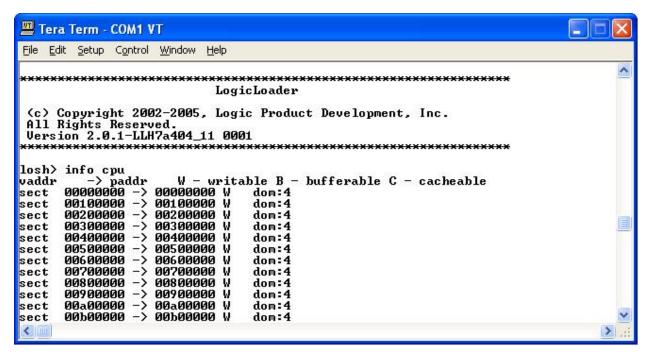

LogicLoader sets up the MMU to remap physical memory to logical memory. Type 'info cpu' at the losh prompt to see how LogicLoader remaps physical memory to logical memory. If you need to address a device outside of the default address map, use the 'remap' command to make additional address space accessible from within LogicLoader.

Figure 1.1: Type "info cpu" to see the MMU remap

Note: the figures you see may differ from those presented in this example.

## 1.3 Physical Hardware Memory Map

Note: memory regions may require the use of the 'remap' command to be accessible.

LH7A400-10 Logical Memory Map during execution of LoLo

for 64M SDRAM 0xFFFFFFF **NOT USED** 0xC4000000 SDRAM 0xC0000000 **RESERVED** 0xB0014000 INTERNAL STATIC MEMORY (80 KB on-chip SRAM) 0xB0000000 0x80003800 ADVANCED HIGH PERFORMANCE BUS REGISTERS 0x80002000 ADVANCED PERIPHERAL BUS REGISTERS 0x80000000 EXTERNAL I/O (FAST) 0x70000000 EXTERNAL I/O (SLOW) 0x60000000 PCMCIA - 2 0x50000000 PCMCIA - 1 0x40000000 NOT USED 0x10000000 FLASH MEMORY

Figure 1.2: LH7A400-10 Hardware Memory Map

0x0000000

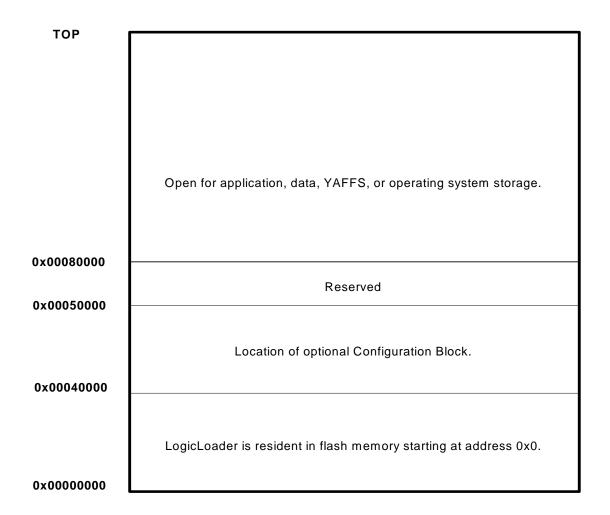

# 1.4 LogicLoader and the Configuration Block in Flash Memory

LogicLoader is programmed into the card engine's resident flash array. The optional Configuration Block may be added with the 'config CREATE' command.

Figure 1.3: Flash Memory Layout

# 1.5 LogicLoader's Location in RAM

LogicLoader executes out of RAM. The diagram below depicts run time location of LogicLoader.

Run-time location of LogicLoader:

At reset, LogicLoader relocates itself from flash memory to system SDRAM. LogicLoader then spends the remainder of its run-time executing out of system SDRAM. Note: the size of LogicLoader's code and variable sections are estimates. This size depends on the exact features built into the Free RAM LogicLoader image and may change with new releases. The location of LogicLoader's stack is dynamically determined at runtime based on the size of the code and variable section. 0xC00C0000 Therefore, the location of the stack is provided as an estimate in Heap and stack for use by LogicLoader this diagram. 0x00040000 LogicLoader variable section Flash block zero LogicLoader code section 0x0000000 0xC0000000 Flash memory System SDRAM

Figure 1.4: LogicLoader RAM Execution Environment

# 2 LH7A400-10 LogicLoader Functionality

# 2.1 Supported Hardware Peripherals

The table below lists LH7A400-10-specific peripherals supported by LogicLoader.

| Hardware Peripheral    | Support<br>(Y/N) | Details                                                         |

|------------------------|------------------|-----------------------------------------------------------------|

| Audio                  | N                | -                                                               |

|                        |                  | LogicLoader supports 8 and 16 bits per pixel; custom displays   |

| Display:               | Υ                | can be supported by using the config block                      |

| LCD-3.5-QVGA-10        | Υ                | Display kit with LCD part number LQ035Q7DB02                    |

| LCD-3.5-QVGA-20        | Υ                | Display kit with LCD part number LQ035Q7DB02                    |

| LCD-5.7-QVGA-10        | Υ                | Display kit with LCD part number LQ057Q3DC02                    |

| LCD-3.6-QVGA-10        | Υ                | Display kit with LCD part number LQ036Q1DA01                    |

| LCD-6.4-VGA-10         | Υ                | Display kit with LCD part number LQ64D343                       |

| LCD-10.4-VGA-10        | Υ                | Display kit with LCD part number LQ10D368                       |

| LCD-12.1-SVGA-10       | Υ                | Display kit with LCD part number LQ121S1DG41                    |

|                        |                  | 10/100MBit support; MAC address stored in dedicated serial      |

|                        |                  | EEPROM; static IP address can be supported by using the         |

| Ethernet               | Y                | config block                                                    |

| Flash Memory           | Υ                | NOR flash only                                                  |

| IrDA                   | N                |                                                                 |

|                        |                  | CompactFlash memory cards are supported only. 16 -> 256MB       |

| Memory Card Expansion: | Υ                | CompactFlash memory cards have been verified.                   |

| IO Mode PCMCIA/ CF     | N                |                                                                 |

| Memory Mode CF         | Υ                | Recommended: SanDisk, Toshiba, PNY                              |

| SD/MMC                 | Υ                |                                                                 |

| Smart Card             | Υ                |                                                                 |

| Processor:             |                  |                                                                 |

| Cache                  | Υ                | Copy-back mode                                                  |

| Clock                  | Υ                | 200MHz CPU / 100MHz Bus                                         |

| Power Management       | N                |                                                                 |

| MMU                    | Υ                | Use 'remap' command to access unmapped regions of memory        |

| PS/2                   | N                |                                                                 |

| RTC                    | N                |                                                                 |

| SDRAM                  | Υ                | 32 or 64 MBytes; CAS-2, auto sizing                             |

| SSP                    | N                |                                                                 |

| Serial Port:           |                  |                                                                 |

|                        |                  | 115200 baud standard, RTS flow only; 2400 to 460800 baud        |

| UARTA                  | Υ                | can be supported by using the config block                      |

| UARTB                  | N                |                                                                 |

| UARTC                  | N                |                                                                 |

| Touch Screen           | N                |                                                                 |

| USB Host               | N                |                                                                 |

| USB Function           | N                |                                                                 |

| Misc:                  |                  |                                                                 |

| GPIO                   | Υ                | Use 'w' and 'x' commands to access data direction and data      |

|                        |                  | registers to control GPIO lines per register description in     |

|                        |                  | processor and IO Controller specification documents.            |

| Status                 | Υ                | Toggles to show system "heartbeat"                              |

| Mode Line 2            | Y                | QuickBoot Feature details: LogicLoader will typically pause 500 |

|                        |                  | mS to look for the 'q' key on UARTA. However, if the Mode Line  |

|                        |                  | 2 (uP_MODE2) is grounded, this 500 mS timeout is skipped and    |

|                        |                  | the boot script runs immediately.                               |

| Serial EEPROM          | Υ                | 128 bytes – use "echo" command to write to /dev/serial_eeprom   |

# 3 Disclaimer

Logic strives to provide the most up to date information. However, the list of supported features in this document is partial and subject to change.

The Supported Options list was created to describe the supported features for fully populated standard card engine builds. If the card engine in use is a custom build or has some hardware feature omitted, the commands related to those hardware features may not function.

If you need software support on demand, please contact Logic Product Development sales at: product.sales@logicpd.com.