Logic Product Development Technical Data

Logic Part Number: 1008209 Rev. A, 10/2007

# MPC8360 COM Express SOM Hardware Specification

© Logic Product Development, 2007. All rights reserved.

# **Table of Contents**

| 1 Introduction                                               |     |

|--------------------------------------------------------------|-----|

| 1.1 Product Brief                                            |     |

| 1.2 Acronyms                                                 |     |

| 1.3 Scope of Document                                        |     |

| 1.4 COM Express Interface                                    |     |

| 1.5 MPC8360 COM Express SOM Block Diagram                    | 5   |

| 1.6 Electrical, Mechanical, and Environmental Specifications |     |

| 1.6.1 Absolute Maximum Ratings                               | 5   |

| 1.6.1.1 Recommended Operating Conditions                     | 6   |

| 2 Electrical Specification                                   |     |

| 2.1 Microcontroller                                          |     |

| 2.1.1 MPC8360E Microcontroller                               | 7   |

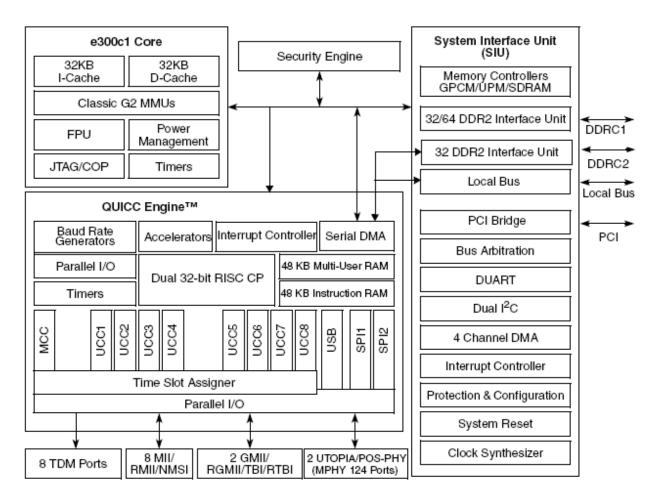

| 2.1.2 MPC8360E Microcontroller Block Diagram                 |     |

| 2.2 Clocks                                                   |     |

| 2.3 Memory                                                   |     |

| 2.3.1 DDR2 SDRAM                                             |     |

| 2.3.2 Direct Memory Access                                   |     |

| 2.3.3 NOR Flash                                              |     |

| 2.3.4 NAND Flash                                             |     |

| 2.4 Ethernet Controllers                                     |     |

| 2.4.1 10/100/1000                                            |     |

| 2.4.2 10/100                                                 |     |

| 2.5 Display Interface                                        |     |

| 2.6 Serial Interfaces                                        |     |

| 2.6.1 UART1                                                  |     |

| 2.6.2 UART2                                                  |     |

| 2.6.3 UART3<br>2.6.4 UART4                                   |     |

|                                                              |     |

| 2.6.5 SPI<br>2.6.6 I2C                                       |     |

| 2.0.0 12C                                                    |     |

| 2.7 OSB Intenace                                             |     |

| 2.6 ADC/Touch Interface                                      |     |

| 2.9 For interface                                            |     |

| 2.10 Centeral Tulpose //O                                    |     |

| 3 System Integration                                         |     |

| 3.1 Configuration                                            |     |

| 3.2 Resets                                                   |     |

| 3.2.1 Master Reset (uP nPORESET)—Reset Input                 |     |

| 3.2.2 SOM Reset (uP_nSRESET)—Reset output                    |     |

| 3.3 Interrupts                                               |     |

| 3.4 JTAG Debugger Interface                                  |     |

| 3.5 Power Management                                         |     |

| 3.5.1 System Power Supplies                                  |     |

| 3.5.1.1 12V                                                  |     |

| 3.5.1.2 VCC5VSB                                              |     |

| 3.5.2 System Power Management                                |     |

| 3.6 ESD Considerations                                       |     |

| 4 Memory and I/O Mapping                                     |     |

| 5 Pin Descriptions and Functions                             |     |

| 5.1 J1A Connector 220-Pin Descriptions                       |     |

| 5.1.1 J1A Row A Pin Descriptions                             | .17 |

| 5.1.2 J1A Row B Pin Descriptions                        | 20 |

|---------------------------------------------------------|----|

| 5.2 J1B Connector 220-Pin Descriptions                  | 24 |

| 5.2.1 J1B Row C Pin Descriptions                        |    |

| 5.2.2 J1B Row D Pin Descriptions                        |    |

| 5.3 Ethernet Signal Link Speeds                         | 30 |

| 6 Differences: COM Express Standard vs. COM Express SOM | 31 |

| 6.1 J1A Row A Differences                               |    |

| 6.2 J1A Row B Differences                               | 31 |

| 6.3 J1B Row C Differences                               |    |

| 6.4 J1B Row D Differences                               |    |

| 7 Mechanical Specifications                             |    |

| 7.1 Interface Connectors                                | 35 |

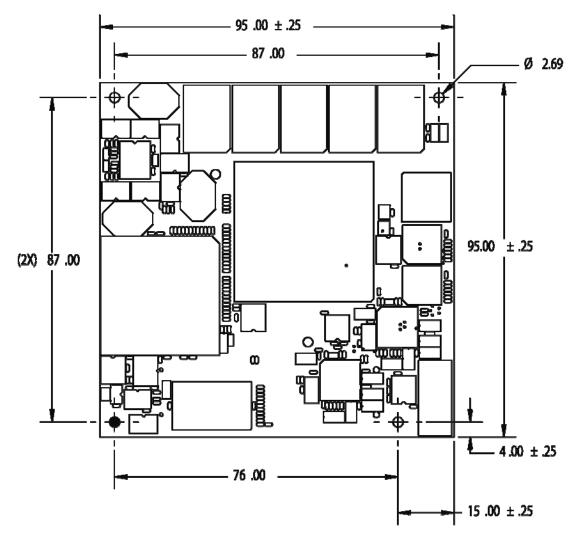

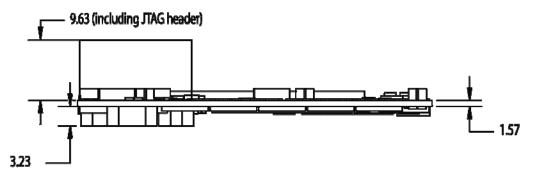

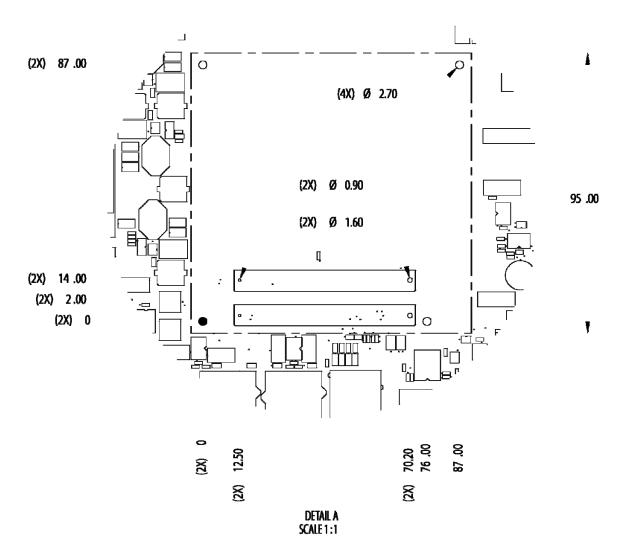

| 7.2 COM Express SOM Mechanical Drawings                 | 35 |

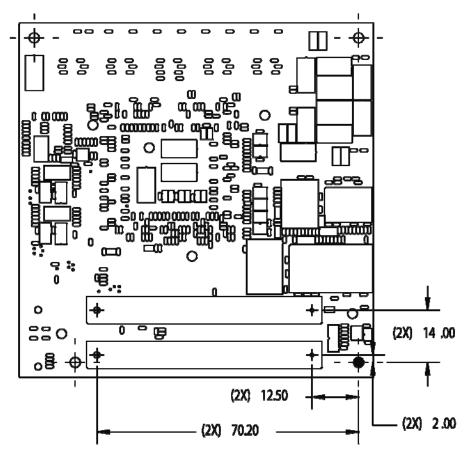

| 7.3 Recommended Baseboard PCB Layout                    | 37 |

| 8 Revision History                                      |    |

# Table of Figures

| Figure 1.1: COM Express SOM Advantages                  | 4  |

|---------------------------------------------------------|----|

| Figure 1.2: MPC8360 COM Express SOM Block Diagram       |    |

| Figure 2.1: MPC8360E Microcontroller Block Diagram      |    |

| Figure 7.1: MPC8360 COM Express SOM Top View            |    |

| Figure 7.2: MPC8360 COM Express SOM Side View           | 36 |

| Figure 7.3: MPC8360 COM Express SOM Bottom View         | 37 |

| Figure 7.4: Baseboard Footprint for the COM Express SOM | 38 |

PRODUCT BRIEF: Logic :: Freescale

# MPC8360 COM Express System on Module

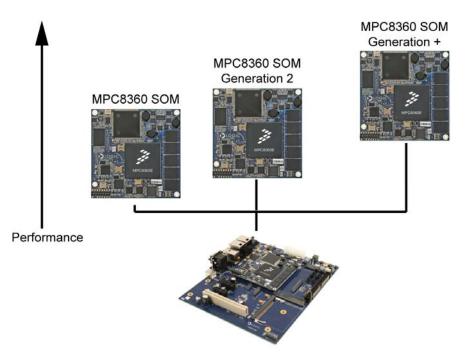

The MPC8360 COM Express System on Module (SOM) is a compact, product-ready hardware and software solution that fast forwards embedded designs.

The MPC8360 SOM adheres to the COM Express Compact form factor and is based on the Type III pin-out specification. This combination offers the essential features for industrial, networking, and medical applications. Using a SOM allows engineers to design a custom baseboard that meets their specific needs and is compatible with other Logic SOMs. This compatibility makes it easy for developers to upgrade their product for greater functionality and performance—while still using their original baseboard design.

By starting with the corresponding Zoom<sup>™</sup> PowerQUICC<sup>™</sup> Development Kit, developers can write application software on the same hardware that will be used in the final product.

The MPC8360 PowerQUICC<sup>™</sup> processor from Freescale Semiconductor provides both control and communications processing in a single chip, making it a cost-effective solution for any product requiring deterministic industrial networking protocols.

MPC8360 COM Express SOM

Designing a product around Logic's SOM allows developers to easily combine their core technologies with the high performance of the MPC8360 PowerQUICC<sup>™</sup> processor.

#### MPC8360 COM EXPRESS :: HIGHLIGHTS:

- + Product-ready SOM with the Freescale PowerQUICC™ MPC8360 processor running at 400 MHz or MPC8360E processor running at 667 MHz

- +COM Express Compact form factor 95 mm x 95 mm x 14.5 mm

- +Long product life-cycle

- +U-Boot bootloader installed in flash

- +Linux Board Support Packages (BSPs)

- +0 °C to 70 °C (commercial temp) or -40 °C to 85 °C (industrial temp)

- +RoHS compliant

#### ZOOM<sup>™</sup> PowerQUICC<sup>™</sup> KIT :: FEATURES:

- + Application baseboard

- + MPC8360 COM Express SOM (COMMPC8360E-10-2752FCR)

- + Production-ready QUICCEngine™ micro-code for PROFIBUS, IEEE(R) 1588, and Ethernet PowerLink available from third-parties

- + Necessary accessories to immediately get up and running

- + Kit available from Freescale (MPC8360E-RDK)

- + See Zoom<sup>™</sup> PowerQUICC<sup>™</sup> Development Kit product brief for more information

### MPC8360 COM Express Ordering Information

|                        | <b>Uputu</b> | SDRAM<br>(MB) | NAND Flash<br>(MB) |   | Graphics/<br>Touch | Ethernet    | Temperature   |

|------------------------|--------------|---------------|--------------------|---|--------------------|-------------|---------------|

| COMMPC8360-10-1652LCR  | 400          | 128           | 64                 | 8 | N                  | 10/100      | 0 ℃ to 70 ℃   |

| COMMPC8360E-10-2752FCR | 667          | 256           | 64                 | 8 | Y                  | 10/100/1000 | 0 °C to 70 °C |

+ Contact Logic for availability of industrial temp configurations.

embedded product solutions

411 N. Washington Ave. Suite 400 Minneapolis, MN 55401 T: 612.672.9495 F: 612.672.9489 I: www.logicpd.com

### ZOOM<sup>™</sup> PowerQUICC<sup>™</sup> Development Kit Ordering Information

| Model Number | COM Express Configuration | Recommended Resale |

|--------------|---------------------------|--------------------|

| MPC8360E-RDK | COMMPC8360E-10-2752FCR    | \$999              |

#### LOGIC WEBSITE :: DESIGN RESOURCES:

- +Logic Technical Support : http://www.logicpd.com/support/

- +Technical Discussion Group : http://www.logicpd.com/support/tdg/

- + Frequently Asked Questions (FAQ) : http://www.logicpd.com/support/fag/

- +For more information contact Logic Sales : product.sales@logicpd.com

#### **Product Features**

#### Processor

+Freescale PowerQUICC<sup>™</sup> MPC8360 processor running at 400 MHz or MPC8360E processor running at 667 MHz

#### SDRAM Memory

+DDR2; 128, 256, 512 MB, or 1 GB +ECC support

#### Flash Memory

+NOR flash; 8 or 16 MB (8 MB standard)

+NAND flash; 64 or 128 MB (64 MB standard)

#### Display

- + Programmable color graphics controller (Fujitsu MB86277)

- +Built-in driver supports up to 1024 x 768 with LVDS interface

- +LVDS can be converted to 18-bit LCD on baseboard

#### Touch Screen

+Integrated 4-wire touch screen controller

#### Network Support

- +Two 10/100 Base-T Ethernet controllers for application/debug

- +Two 10/100/1000 Base-T Ethernet controllers for application/debug

#### PC Card Expansion

+32-bit PCI connection

+Four USB 2.0 full-speed host interfaces

#### Serial Ports

+Four 16C550 compatible UARTs

#### GPIO

+Programmable I/O depending on peripheral requirements

#### Software

+U-Boot bootloader +Linux BSP

#### Mechanical

+COM Express Compact form factor 95 mm wide x 95 mm long x 14.5 mm high

**RoHS** Compliant

© 2007 Logic Product Development. All rights reserved.

PN: 1007946 Rev B

## 1.2 Acronyms

#### 1.3 Scope of Document

This Hardware Specification is unique to the design and use of the MPC8360 COM Express SOM as designed by Logic and does not intend to include information outside of that scope. Detailed information about the Freescale MPC8360E PowerQUICC processor or any other device component on the COM Express SOM can be found in their respective manuals and specification documents. Specific documents mentioned within this Hardware Specification include:

- MPC8360 COM Express SOM Schematics (available from Logic at <a href="http://www.logicpd.com/auth/">http://www.logicpd.com/auth/</a>)

- MPC8360E PowerQUICC<sup>TM</sup> II Pro Integrated Communications Processor Family Reference Manual (hereafter refered to as MPC8360E Processor Reference Manual, available from Freescale at <u>http://www.freescale.com/PowerQUICC</u>)

- MB86277 <MINT> Graphics Controller Specifications (available from Fujitsu's website)

- USB 2.0 Specification (available from USB.org at <a href="http://www.usb.org/developers/docs/">http://www.usb.org/developers/docs/</a>)

- PCI Local Bus Specification

#### 1.4 COM Express Interface

Logic's common COM Express interface allows for easy migration to new processors and technology. Logic is constantly researching and developing new technologies to improve performance, lower cost, and increase feature capabilities. By using the common COM Express footprint, it is possible to take advantage of Logic's work without having to re-spin the old design. Contact Logic sales for more information.

In fact, encapsulating a significant amount of a product design onto the COM Express SOM reduces any long-term risk of obsolescence. If a component on the COM Express SOM design becomes obsolete, Logic will design for an alternative part that is transparent to the end-product. Furthermore, Logic tests all modules prior to delivery, decreasing time-to-market and ensuring a simpler and less costly manufacturing process.

Figure 1.1: COM Express SOM Advantages

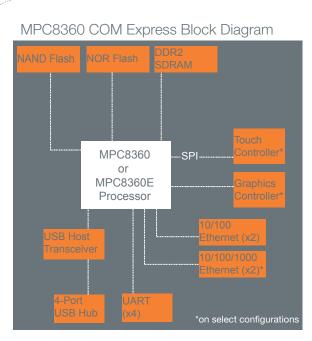

### 1.5 MPC8360 COM Express SOM Block Diagram

#### Figure 1.2: MPC8360 COM Express SOM Block Diagram

#### **1.6** Electrical, Mechanical, and Environmental Specifications

#### 1.6.1 Absolute Maximum Ratings

| Parameter             | Symbol  | Rating         | Unit |

|-----------------------|---------|----------------|------|

| DC 12V Supply Voltage | 12V     | VSS-0.3 to 15  | V    |

| Standby Voltage       | VCC5VSB | VSS-0.3 to 5.5 | V    |

**NOTE:** These stress ratings are only for transient conditions. Operation at, or beyond, absolute maximum rating conditions may affect reliability and cause permanent damage to the SOM and its components.

| Parameter                        | Min        | Typical        | Max        | Unit   | Notes |

|----------------------------------|------------|----------------|------------|--------|-------|

| DC 12V Input Voltage             | 9.6        | 12             | 14.4       | V      |       |

| DC 12V Active Current            | —          | —              | —          | mA     |       |

| DC 12V Suspend Current           | —          | —              | —          | mA     |       |

| DC 12V Standby Current           | —          | —              | —          | mA     |       |

| Standby Voltage                  | 4.5        | 5              | 5.5        | V      |       |

| DC 5V Active Current             | —          | —              | —          | mA     |       |

| DC 5V Suspend Current            | —          | —              | —          | mA     |       |

| DC 5V Standby Current            | —          | —              | —          | mA     |       |

| Commercial Operating Temperature | 0          | 25             | 70         | °C     |       |

| Storage Temperature              | -40        | 25             | 85         | °C     |       |

| Dimensions                       | _          | 95 x 95 x 14.5 | _          | mm     |       |

| Weight                           | —          | 65             | —          | Grams  | 1     |

| Connector Insertion/Removal      | —          | 30             | —          | Cycles |       |

| Input Signal High Voltage        | 0.8 x VREF | —              | VREF       | V      | 2     |

| Input Signal Low Voltage         | GND        | —              | 0.2 x VREF | V      | 2     |

| Output Signal High Voltage       | 0.8 x VREF | —              | VREF       | V      | 2     |

| Output Signal Low Voltage        | GND        | _              | 0.2 x VREF | V      | 2     |

#### **Recommended Operating Conditions** 1.6.1.1

Notes:

- 1.

- May vary depending on COM Express configuration. VREF represents the peripheral I/O supply reference for the specific CPU voltage rail. 2.

# 2 Electrical Specification

#### 2.1 Microcontroller

#### 2.1.1 MPC8360E Microcontroller

The MPC8360 COM Express SOM uses Freescale's highly integrated MPC8360E processor. This device features the e300c1 core and provides many integrated on-chip peripherals, including (as listed in Freescale's *MPC8360E Processor Reference Manual*):

- e300c1 Power Architecture<sup>™</sup> processor core

- □ Enhanced version of the MPC603e core

- High-performace, superscaler processor core with a four-stage pipeline and low interrupt latency times

- $\hfill\square$  Floating-point, integer, load/store, system register, and branch processing units

- □ 32-Kbyte instruction cache and 32-Kbyte data cache with lockable capabilities

- Dynamic power management

- Enhanced hardware program debug features

- Software-compatible with Freescale processor families implementing Power Architecture technology

- Separate PLL that is clocked by the system bus clock

- QUICC Engine 2.0 block

- Two 32-bit RISC controllers for flexible support of the communications peripherals with the following features:

- One clock per instruction

- Separate PLL for operating frequency that is independent of system's bus and core frequency for power and performance optimization

- 32-bit instruction object code

- Executes code from internal ROM or RAM

- □ 32-bit arithmetic logic unit (ALU) data path

- Modular architecture allowing for easy functional enhancements

- Slave bus for CPU access of registers and multiuser RAM space

- a 48 Kbytes of instruction RAM

- 48 Kbytes of multiuser data RAM

- □ QE peripheral request interface (for SEC, PCI, and IEEE Std. 1588<sup>™</sup>)

- Eight universal communication controllers (UCCs)

- ATM controller

- Universal serial bus (USB) controller

- Many general purpose I/O (GPIO) signals

- 2 serial DMA channels

- Time slot assigner and 8 TDM serial interfaces

See Freescale's MPC8360E Processor Reference Manual for additional information.

**IMPORTANT NOTE:** Please visit <u>http://www.freescale.com/PowerQUICC</u> for errata on the MPC8360E processor and documentation.

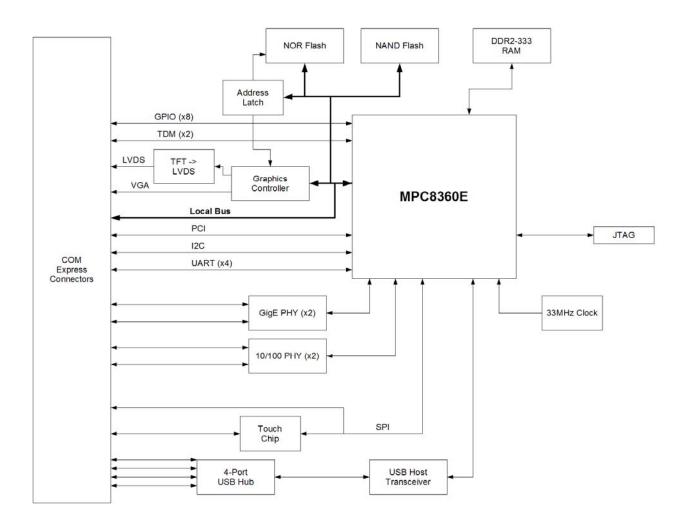

#### 2.1.2 MPC8360E Microcontroller Block Diagram

Figure 2.1: MPC8360E Microcontroller Block Diagram

#### 2.2 Clocks

The MPC8360E requires an oscillator to enable proper internal timing. A 33.33 MHz oscillator is used to generate the processor's internal clocks through a series of PLLs. To generate the core CPU clock, the 33.33 MHz signal is run through a System PLL controlled by the value set in the Reset Configuration Words. The output of the System PLL is used to supply the Core PLL as well as the timing units for the Local Bus and the DDR memory controller. There is also a separate PLL for the QUICC Engine clock which is also based off the 33.33 MHz oscillator input.

**IMPORTANT NOTE:** Please see Freescale's *MPC8360E Processor Reference Manual* for additional information about processor clocking.

The MPC8360E clock speeds are set in the Reset Configuraton Words (RCW). The RCW can be changed to allow different clock speeds.

The MPC8360 COM Express SOM provides two external bus clocks, uP\_LCLK1 and uP\_LCLK2. These clocks are enabled by default. uP\_LCLK0 is the clock used for the onboard graphics controller. uP\_SDCLK[0:4]+/- serve as the DDR2 SDRAM clocks on the MPC8360 COM Express SOM.

#### 2.3 Memory

#### 2.3.1 DDR2 SDRAM

The MPC8360 COM Express SOM uses a 64-bit memory bus to interface to DDR2 SDRAM. The MPC8360 COM Express SOM can handle configurations of 128 Mbytes, 256 Mbytes, 512 Mbytes, or 1 Gbytes SDRAM in order to meet the user's memory requirements and cost constraints. Logic's default memory configuration on the COM Express SOM included in the Development Kit is 256 Mbytes.

The MPC8360 COM Express SOM also has support for multi-bit error detection and single bit error detection and correction ECC.

#### 2.3.2 Direct Memory Access

The Freescale MPC8360E microcontroller has a direct memory access (DMA) controller which contains 4 DMA channels for use with internal peripherals to achieve highly efficient data throughput. For more information on using the DMA interface, please refer to the *MPC8360E Processor Reference Manual*.

#### 2.3.3 NOR Flash

The MPC8360 COM Express SOM uses a 16-bit memory bus to interface to NOR flash memory. The onboard memory can be configured as 8 or 16 Mbytes to meet the user's flash requirements and cost constraints. Logic's default flash configuration is 8 Mbytes on the COM Express SOM included in the Zoom PowerQUICC Development Kit.

#### 2.3.4 NAND Flash

The MPC8360 COM Express SOM uses an 8-bit memory bus to interface to NAND flash. The product supports configurations of 64 or 128 Mbytes. The COM Express SOM included in the standard Zoom PowerQUICC Development Kit contains 64 Mbytes of NAND flash.

It is possible to expand the SOM's non-volatile storage capability by adding external NOR flash or NAND flash. Please refer to the *MPC8360 COM Express SOM Schematics* for reference designs or contact Logic for other possible peripheral designs.

#### 2.4 Ethernet Controllers

#### 2.4.1 10/100/1000

The MPC8360 COM Express SOM uses two Broadcom BCM5481 Ethernet transceivers to provide an easy-to-use Gigabit networking interface. Please note the TRDx+/- pairs must be routed as differential pairs on the baseboard printed circuit board (PCB).

#### 2.4.2 10/100

Two National DP83848 Ethernet transceivers provide the 10/100 networking interface on the MPC8360 COM Express SOM. Please note the TD+/- and RD+/- pairs must be routed as differential pairs on the baseboard PCB.

#### 2.5 Display Interface

The MPC8360 COM Express SOM uses the Fujitsu MB86277 (MINT) graphics controller. The MINT supports display resolutions up to 1024 x 768 at 24 bpp. Please refer to the *MB86277 <MINT> Graphics Controller Specifications* for further information on the graphics controller. The signals from the MINT graphics controller are provided in 24-bit digital RGB and analog RGB. The digital RGB is converted to LVDS format. Both LVDS and analog RGB are available through the expansion connectors. Logic has written drivers for numerous display panels of different types and sizes. Please contact Logic before selecting a panel for your application.

#### 2.6 Serial Interfaces

The MPC8360 COM Express SOM comes with the following serial channels: UART1, UART2, UART3, UART4, SPI, and I2C. If additional serial channels are required, please contact Logic for reference designs. Please see the *MPC8360E Processor Reference Manual* for further information regarding serial communications.

#### 2.6.1 UART1

UART1 has been configured to be the MPC8360 Development Kit's main serial port. It is an asynchronous PC16550D-compatible UART. This UART provides a high-speed serial interface that uses First In / First Out (FIFO) and is capable of sending and receiving serial data simultaneously. The signals from the COM Express SOM are Transistor-Transistor Logic (TTL) level signals, not RS232 level signals. The user must provide an external RS232 transceiver for RS232 applications. Logic has provided an example baseboard reference design with the Zoom PowerQUICC Development Kit. When choosing an RS232 transceiver, the user should keep in mind cost, availability, ESD protection, and data transfer rates.

The UART1 baud rate is set by default to 115.2 Kbits/sec, though it supports most common serial baud rates.

#### 2.6.2 UART2

Serial Port UART2 is an asynchronous PC16550D-compatible UART. This UART is a high-speed serial interface that uses FIFO and is capable of sending and receiving serial data simultaneously. The signals from the MPC8360 COM Express SOM are TTL level signals, not RS232 level signals. The UART2 baud rate can also be set to most common serial baud rates.

#### 2.6.3 UART3

Serial Port UART3 is an asynchronous UART. This UART is a high-speed serial interface that uses FIFO and is capable of sending and receiving serial data simultaneously. The signals from the MPC8360 COM Express SOM are TTL level signals, not RS232 level signals. The UART3 baud rate can also be set to most common serial baud rates.

#### 2.6.4 UART4

Serial Port UART4 is an asynchronous UART. This UART is a high-speed serial interface that uses FIFO and is capable of sending and receiving serial data simultaneously. The signals from the MPC8360 COM Express SOM are TTL level signals, not RS232 level signals. The UART4 baud rate can also be set to most common serial baud rates.

#### 2.6.5 SPI

There are two Serial Peripheral Interface (SPI) ports on the MPC8360 COM Express SOM. The first port communicates with the onboard EEPROM and touch chip. It is also available through the expansion connectors. The second port communicates to the Ethernet transceivers. Please see the *MPC8360E Processor Reference Manual* for further information.

#### 2.6.6 I2C

The MPC8360 COM Express SOM supports two external I2C ports. For both ports, the clock and data signals have 2.2K pull-up resistors to 3.3V. Please see the *MPC8360E Processor Reference Manual* for further information.

#### 2.7 USB Interface

The MPC8360 COM Express SOM supports four USB 2.0 full-speed host ports. All ports can operate up to 12 Mbytes/sec. The MPC8360E processor has an internal USB controller. The MPC8360 COM Express SOM has an external NXP ISP1105 transceiver to support a single port. The single port coming out of the ISP1105 is fed into a NXP ISP1520 4-port hub. For more information on using the USB interface, please see the *MPC8360E Processor Reference Manual*.

**IMPORTANT NOTE:** In order for USB to be correctly implemented on the MPC8360 COM Express SOM, additional impedance matching circuitry may be required on the USBx+ and USBx- signals before they can be used. USB 2.0 requirements specify the signals must be routed as differential pairs with a 90-ohm differential impedance. Refer to the USB 2.0 Specification for detailed information.

#### 2.8 ADC/Touch Interface

The MPC8360 COM Express SOM uses an Analog Devices AD7843 for the touch screen controller (TSC). The controller includes a 12-bit analog-to-digital converter (ADC). This TSC is used to support standard 4-wire resistive touch panels. The TSC has two A/D signals that are externally available through the expansion connectors. The device is connected to the CPU by the SPI interface.

#### 2.9 PCI Interface

The MPC8360E processor is compatible with the *PCI Local Bus Specification*, Rev. 2.2. The MPC8360 COM Express SOM operates in host mode. Please refer to the *MPC8360E Processor Reference Manual* for more information.

#### 2.10 General Purpose I/O

Logic designed the MPC8360 COM Express SOM to be flexible and provide multiple options for digital General Purpose I/Os (GPIO). There are numerous digital GPIO pins on the MPC8360 COM Express SOM that interface to the MPC8360E processor. See the "Pin Descriptions and Functions" Section of this Hardware Specification for more information. If certain peripherals are not desired, such as UARTs or PCI, then multiple GPIO pins become available for custom use.

#### 2.11 Expansion/Feature Options

The MPC8360 COM Express SOM was designed for expansion and a variable feature set, providing all the necessary control signals and bus signals to expand the user's design. It is possible for a user to

expand the SOM's functionality even further by adding local bus devices. Logic has experience implementing additional options, including audio codecs, Ethernet ICs, co-processors, and components on SOMs. Please contact Logic for potential reference designs before selecting your peripherals.

# 3 System Integration

#### 3.1 Configuration

The MPC8360 COM Express SOM was designed to meet multiple applications for users with specific design and budget requirements. As a result, this SOM supports a variety of embedded operating systems and supports the following custom hardware configurations:

- Flexible memory footprint: 128, 256, 512 Mbytes, or 1 Gbyte DDR2 SDRAM

- Flexible NOR flash footprint: 8 or 16 Mbytes NOR flash

- Flexible NAND flash footprint: 64 or 128 Mbytes NAND flash

- Optional Broadcom BCM5481 10/100/1000 Ethernet transceiver(s)

- Optional National DP83848 10/100 Ethernet transceiver(s)

- Optional Fujitsu MB86277 (MINT) graphics controller

Please contact Logic for additional hardware configurations to meet your application needs.

#### 3.2 Resets

The MPC8360 COM Express SOM has a reset input (uP\_nPORESET) and a reset output (uP\_nSRESET). External devices use uP\_nPORESET to assert reset to the product. The SOM uses uP\_nSRESET to indicate to other devices that the SOM is in reset.

#### 3.2.1 Master Reset (uP\_nPORESET)—Reset Input

Logic suggests that custom designs implementing the MPC8360 COM Express SOM specify the uP\_nPORESET signal as the "pin hole" reset used in commercial embedded systems. The uP\_nPORESET triggers a power-on-reset event to the MPC8360E processor and resets the entire CPU.

**IMPORTANT NOTE:** Any custom reset circuit design should guard the assertion of the reset lines during a low power state so as to prevent power-up in a low or bad power condition. Powering-up in a low or bad power condition will cause data corruption and possible temporary system lockup.

A low pulse on the uP\_nPORESET signal, asserted by an external source (for example, the reset button on the custom design application) will bring uP\_nPORESET low until the assertion source is de-asserted. There is no delay beyond the de-assertion of the external uP\_nPORESET signal source, so the custom design must ensure that the assertion time is sufficient for all related peripherals.

Logic suggests that for any external assertion source that triggers the uP\_nPORESET signal, analog or digital, use de-bouncing to generate a clean, one-shot reset signal.

#### 3.2.2 SOM Reset (uP\_nSRESET)—Reset output

All hardware peripherals should connect their hardware-reset pin to the uP\_nSRESET signal on the expansion connector, unless the peripheral is needed to fetch the Reset Configuration Words (RCW). If needed for the RCW, the peripheral should be connected to uP\_nPORESET. Internally all MPC8360 COM Express SOM peripheral hardware reset pins are connected to the uP\_nSRESET net (except NOR flash because of the power-up sequence).

#### 3.3 Interrupts

The MPC8360 COM Express SOM uses the integrated programmable interrupt controller (IPIC). The IPIC prioritizes and manages interrupts from both internal and external sources. Refer to Freescale's *MPC8360E Processor Reference Manual* for further information on using interrupts.

#### 3.4 JTAG Debugger Interface

The JTAG connection on the MPC8360 COM Express SOM allows recovery of corrupted flash memory and real-time application debug. There are several third-party JTAG debuggers available for Freescale microcontrollers. The following signals make up the JTAG interface to the MPC8360 COM Express SOM: uP\_TDI, uP\_TMS, uP\_TCK, uP\_TDO, nCKSTOP\_OUT, nCKSTOP\_IN, COP\_nTRST, and uP\_nHRESET. These signals interface directly to a 16-pin 0.1" connector, shown as reference designator J2 on the *MPC8360 COM Express SOM Schematics*.

#### 3.5 Power Management

#### 3.5.1 System Power Supplies

The MPC8360 COM Express SOM has two power areas: 12V and VCC5VSB. All power areas are inputs to the MPC8360 COM Express SOM.

#### 3.5.1.1 12V

The 12V input is the main source of power for the MPC8360 COM Express SOM. This input expects a voltage between 9.6V and 14.4V, with 12V as the standard. The 12V input is passed through several buck converters to create all onboard voltages. This supply must stay within the acceptable levels specified in Section 2 of this manual, "Electrical Specification", unless experiencing power down or critical power conditions.

#### 3.5.1.2 VCC5VSB

The VCC5VSB voltage powers the power button circuit. The baseboard should provide 5V to VCC5VSB at all times. VCC5VSB also generates 5V for the USB hub circuit. VCC5VSB must stay within the acceptable levels specified in Section 2 of this manual, "Electrical Specification".

#### 3.5.2 System Power Management

Good power management design is important in any system development and embedded system design is no exception. In embedded system design, power management is typically one of the most complicated areas due to the dramatic effect it has on the product cost, performance, usability, and overall customer satisfaction. Many factors affect a power-efficient hardware design: power supply selection (efficiency), clocking design, IC and component selection, etc. The MPC8360 COM Express SOM was designed to keep these aspects in mind while providing maximum flexibility in software and system integration.

On the MPC8360 COM Express SOM there are many different software configurations that drastically affect power consumption: microcontroller core clock frequency, bus clock frequency, peripheral clocks, bus modes, power management states (dynamic power management, shutting down unused blocks, software-controlled power-down states), peripheral power states and modes, product user scenarios, interrupt handling, and display settings (resolution, backlight, refresh, bits per pixel). These settings are typically initialized in the startup software routines and may be later modified in the operating system and

application software. Information for these items can be found in the appropriate documents such as the Freescale *MPC8360E Processor Reference Manual* or the specific software BSP manual.

#### 3.6 ESD Considerations

The MPC8360 COM Express SOM was designed to interface to a customer's peripheral board, while remaining low cost and adaptable to different applications. As such, the MPC8360 COM Express SOM does not provide any onboard ESD protection circuitry—this must be provided by the end-product it is used in. Logic has extensive experience in designing products with ESD requirements. Please contact Logic if you need any assistance in ESD design considerations.

# 4 Memory and I/O Mapping

On the Freescale MPC8360E microcontroller, all address mapping for the local bus and external chip selects is configurable. Please consult Freescale's *MPC8360E Processor Reference Manual* for details.

#### **DDR2 SDRAM**

The MPC8360E processor contains dedicated chip selects for the DDR2 SDRAM interface. MEMC1\_MCS0 is used as the chip select for the DDR2 SDRAM on the MPC8360 COM Express SOM.

#### Local Bus

Mapped chip select signals for the Local Bus are available as outputs from the microcontroller and are assigned as follows:

LCS0\* = NOR flash LCS1 = NAND flash LCS2 = Graphics Controller LCS3\* = Available for use by an off-board external device (BOOT\_nCS) LCS4 = Available for use by an off-board external device (uP\_nLCS4) LCS5 = Available for use by an off-board external device (uP\_nLCS5) \*LCS0 and LCS3 connection is controlled by MODE3. When MODE3 is bit

\*LCS0 and LCS3 connection is controlled by MODE3. When MODE3 is high, LCS0 connects to NOR flash and LCS3 goes to the expansion connectors; When MODE3 is low, LCS0 connects to the expansion connectors and LCS3 goes to the NOR flash.

# 5 Pin Descriptions and Functions

**IMPORTANT NOTE:** The following pin descriptions and states are described after the initialization of uBoot (bootloader). Many of the signals defined in the tables below can be configured as input or outputs—all GPIOs on the MPC8360E processor can be configured as input, output, input/output, or disabled—and have different functions. It is critical to review all signals in the final design (both electrical and software) to verify the necessary configuration (external pull-ups/pull-downs).

## 5.1 J1A Connector 220-Pin Descriptions

#### 5.1.1 J1A Row A Pin Descriptions

| J1A      |             |     |         |                                                                                                                |

|----------|-------------|-----|---------|----------------------------------------------------------------------------------------------------------------|

| Pin#     | Signal Name | I/O | Voltage | Description                                                                                                    |

| A1       | GND         | I   | GND     | Ground. Connect to digital ground.                                                                             |

|          |             |     |         | Gigabit Ethernet 1 transmit/receive pair 3. Route as differential pair                                         |

|          |             |     |         | with ENET1_TRD3+. Requires external magnetics. See example                                                     |

| A2       | ENET1_TRD3- | I/O | 3.3V    | FlexATX baseboard design for reference components.                                                             |

|          |             |     |         | Gigabit Ethernet 1 transmit/receive pair 3. Route as differential pair                                         |

|          |             |     |         | with ENET1_TRD3 Requires external magnetics. See example                                                       |

| A3       | ENET1_TRD3+ | I/O | 3.3V    | FlexATX baseboard design for reference components.                                                             |

|          |             | ~   | a a) (  | This signal is used with ENET1_LED1 to determine the Ethernet 1 link                                           |

| A4       | ENET1_LED2  | 0   | 3.3V    | speed. See Section 5.3.                                                                                        |

|          |             |     | 0.01/   | This signal is used with ENET1_LED2 to determine the Ethernet 1 link                                           |

| A5       | ENET1_LED1  | 0   | 3.3V    | speed. See Section 5.3.                                                                                        |

|          |             |     |         | Gigabit Ethernet 1 transmit/receive pair 2. Route as differential pair                                         |

|          |             |     | 0.01/   | with ENET1_TRD2+. Requires external magnetics. See example                                                     |

| A6       | ENET1_TRD2- | I/O | 3.3V    | FlexATX baseboard design for reference components.                                                             |

|          |             |     |         | Gigabit Ethernet 1 transmit/receive pair 2. Route as differential pair                                         |

| A7       | ENET1 TRD2+ | I/O | 3.3V    | with ENET1_TRD2 Requires external magnetics. See example<br>FlexATX baseboard design for reference components. |

| A7<br>A8 | NC          | NC  | NA      | No connect. Do not connect.                                                                                    |

| Ao       | NC          | INC | INA     | Gigabit Ethernet 1 transmit/receive pair 1. Route as differential pair                                         |

|          |             |     |         | with ENET1_TRD1+. Requires external magnetics. See example                                                     |

| A9       | ENET1 TRD1- | I/O | 3.3V    | FlexATX baseboard design for reference components.                                                             |

| АЭ       |             | 1/0 | 5.5V    | Gigabit Ethernet 1 transmit/receive pair 1. Route as differential pair                                         |

|          |             |     |         | with ENET1 TRD1 Requires external magnetics. See example                                                       |

| A10      | ENET1 TRD1+ | I/O | 3.3V    | FlexATX baseboard design for reference components.                                                             |

| A11      | GND         |     | GND     | Ground. Connect to digital ground.                                                                             |

| /        |             |     |         | Gigabit Ethernet 1 transmit/receive pair 0. Route as differential pair                                         |

|          |             |     |         | with ENET1_TRD0+. Requires external magnetics. See example                                                     |

| A12      | ENET1 TRD0- | I/O | 3.3V    | FlexATX baseboard design for reference components.                                                             |

|          |             |     | 0.01    | Gigabit Ethernet 1 transmit/receive pair 0. Route as differential pair                                         |

|          |             |     |         | with ENET1 TRD0 Requires external magnetics. See example                                                       |

| A13      | ENET1 TRD0+ | I/O | 3.3V    | FlexATX baseboard design for reference components.                                                             |

|          | -           |     |         | Gigabit Ethernet 1 center tap. This signal is the reference voltage for                                        |

|          |             |     |         | Etherenet 1 magnetics center tap. See example FlexATX baseboard                                                |

| A14      | ENET1 CT    | 0   | 2.5V    | design for reference components.                                                                               |

|          |             |     |         | Reserved for future use. Connected to GPIO PD13 of the MPC8360.                                                |

| A15      | GPIO_PD13   | I/O | 3.3V    | See Note 1 at the bottom of this table.                                                                        |

| A16      | NC          | NC  | NA      | Reserved for future use. Do not connect.                                                                       |

| A17      | NC          | NC  | NA      | Reserved for future use. Do not connect.                                                                       |

|          |             |     |         | Reserved for future use. Connected to GPIO_PD19 of the MPC8360.                                                |

| A18      | GPIO_PD19   | I/O | 3.3V    | See Note 1 at the bottom of this table.                                                                        |

| A19      | NC          | NC  | NA      | Reserved for future use. Do not connect.                                                                       |

| A20      | NC          | NC  | NA      | Reserved for future use. Do not connect.                                                                       |

| A21      | GND         | I   | GND     | Ground. Connect to digital ground.                                                                             |

| J1A<br>Pin# | Signal Name        | I/O | Voltage      | Description                                                                                                                                                                                                                                                                                |

|-------------|--------------------|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A22         | NC                 | NC  | NA           | Reserved for future use. Do not connect.                                                                                                                                                                                                                                                   |

| A23         | NC                 | NC  | NA           | Reserved for future use. Do not connect.                                                                                                                                                                                                                                                   |

|             |                    |     |              | Active low. This signal is used to turn the 12V power rail on and off.<br>When low, the 12V supply is on. When high, the 12V supply is off. It<br>can be connected directly to an ATX supply's nPS_ON signal. If not<br>used with an ATX supply, a pull-up resistor to VCC5VSB is required |

| A24         | nPS_ON             | 0   | 3.3V         | on the baseboard.                                                                                                                                                                                                                                                                          |

| A25         | NC                 | NC  | NA           | Reserved for future use. Do not connect.                                                                                                                                                                                                                                                   |

| A26         | NC                 | NC  | NA           | Reserved for future use. Do not connect.                                                                                                                                                                                                                                                   |

|             |                    |     |              | Reserved for future use. Connected to GPIO_PD22 of the MPC8360.                                                                                                                                                                                                                            |

| A27         | GPIO PD22          | I/O | 3.3V         | See Note 1 at the bottom of this table.                                                                                                                                                                                                                                                    |

| A28         | NC                 | NC  | NA           | Reserved for future use. Do not connect.                                                                                                                                                                                                                                                   |

|             |                    |     |              | TDM 1 receive data. See Freescale's MPC8360E Processor                                                                                                                                                                                                                                     |

| A29         | TDM1_RXD           | I/O | 3.3V         | Reference Manual for more information.                                                                                                                                                                                                                                                     |

|             |                    |     |              | TDM 1 transmit data. See Freescale's MPC8360E Processor                                                                                                                                                                                                                                    |

| A30         | TDM1 TXD           | I/O | 3.3V         | Reference Manual for more information.                                                                                                                                                                                                                                                     |

| A31         | GND                | 1   | GND          | Ground. Connect to digital ground.                                                                                                                                                                                                                                                         |

| / 10 1      |                    | '   | OND .        | Reserved for future use. Connected to GPIO_PD24 of the MPC8360.                                                                                                                                                                                                                            |

| A32         | GPIO PD24          | I/O | 3.3V         | See Note 1 at the bottom of this table.                                                                                                                                                                                                                                                    |

| / 102       |                    |     | 0.01         | Reserved for future use. Connected to GPIO_PD25 of the MPC8360.                                                                                                                                                                                                                            |

| A33         | GPIO PD25          | I/O | 3.3V         | See Note 1 at the bottom of this table.                                                                                                                                                                                                                                                    |

| / 100       |                    |     | 0.0 V        | Reserved for future use. Connected to GPIO_PD27 of the MPC8360.                                                                                                                                                                                                                            |

| A34         | GPIO PD27          | I/O | 3.3V         | See Note 1 at the bottom of this table.                                                                                                                                                                                                                                                    |

| A35         | NC                 | NC  | NA           | Reserved for future use. Do not connect.                                                                                                                                                                                                                                                   |

| 700         |                    | 110 |              | SPI interface chip select. When the MPC8360 is in master mode,                                                                                                                                                                                                                             |

|             |                    |     |              | indicates a multiple-master error. In slave mode, acts as a chip select.                                                                                                                                                                                                                   |

| A36         | uP SPI nSEL        | I/O | 3.3V         | Pulled up to 3.3V_IO_VDD through a 10K resistor.                                                                                                                                                                                                                                           |

| A30<br>A37  | uP_SPI_CLK         |     | 3.3V<br>3.3V | SPI interface clock. Pulled up to 3.3V_IO_VDD through a 10K resistor.                                                                                                                                                                                                                      |

| A37         |                    | 1/0 | 3.3V         | IEEE1588 Real Time Clock pulse per second output 3. See                                                                                                                                                                                                                                    |

|             |                    |     |              | Freescale's MPC8360E Processor Reference Manual for more                                                                                                                                                                                                                                   |

| A38         | PTP PPS3           | о   | 3.3V         | information.                                                                                                                                                                                                                                                                               |

| A30         |                    | 0   | 5.5V         | IEEE1588 Real Time Clock pulse per second output 2. See                                                                                                                                                                                                                                    |

|             |                    |     |              | Freescale's MPC8360E Processor Reference Manual for more                                                                                                                                                                                                                                   |

| A39         | PTP PPS2           | 0   | 3.3V         | information.                                                                                                                                                                                                                                                                               |

| / 100       | <u>     _   02</u> |     | 0.01         | IEEE1588 Real Time Clock pulse per second output 1. See                                                                                                                                                                                                                                    |

|             |                    |     |              | Freescale's MPC8360E Processor Reference Manual for more                                                                                                                                                                                                                                   |

| A40         | PTP PPS1           | 0   | 3.3V         | information.                                                                                                                                                                                                                                                                               |

| A41         | GND                |     | GND          | Ground. Connect to digital ground.                                                                                                                                                                                                                                                         |

| / (+ 1      |                    |     | GIND         | USB host port 2 data minus signal. Route as differential pair with                                                                                                                                                                                                                         |

|             |                    |     |              | USB2+. Follow USB 2.0 routing guidelines. Route pair with 90 ohms                                                                                                                                                                                                                          |

| A42         | USB2-              | I/O | 3.3V         | differntial impedance.                                                                                                                                                                                                                                                                     |

| / (+2       | 00BZ               |     | 0.01         | USB host port 2 data plus signal. Route as differential pair with USB2-                                                                                                                                                                                                                    |

|             |                    |     |              | . Follow USB 2.0 routing guidelines. Route pair with 90 ohms                                                                                                                                                                                                                               |

| A43         | USB2+              | I/O | 3.3V         | differntial impedance.                                                                                                                                                                                                                                                                     |

| , (10       | COB2.              |     | 0.01         | Active low. USB host ports 2 and 3 over current flag. Indicates an over                                                                                                                                                                                                                    |

|             |                    |     |              | current condition exists on the USB host port(s). Pulled up to                                                                                                                                                                                                                             |

| A44         | USB2_nOC           |     | 3.3V         | 3.3V_IO_VDD through a 10K resistor.                                                                                                                                                                                                                                                        |

|             |                    | ľ   |              | USB host port 0 data minus signal. Route as differential pair with                                                                                                                                                                                                                         |

|             |                    |     |              | USB0+. Follow USB 2.0 routing guidelines. Route pair with 90 ohms                                                                                                                                                                                                                          |

| A45         | USB0-              | I/O | 3.3V         | differntial impedance.                                                                                                                                                                                                                                                                     |

|             |                    |     |              | USB host port 0 data plus signal. Route as differential pair with USB0-                                                                                                                                                                                                                    |

|             |                    |     |              | . Follow USB 2.0 routing guidelines. Route pair with 90 ohms                                                                                                                                                                                                                               |

| A46         | USB0+              | I/O | 3.3V         | differntial impedance.                                                                                                                                                                                                                                                                     |

| A40<br>A47  | NC                 | NC  | NA           | No connect. Do not connect.                                                                                                                                                                                                                                                                |

| /1+/        |                    |     |              | IEEE1588 Real Time Clock input trigger to capture timestamps 1. See                                                                                                                                                                                                                        |

|             |                    |     |              | Freescale's MPC8360E Processor Reference Manual for more                                                                                                                                                                                                                                   |

| A48         | PTP EXT TRIG1      |     | 3.3V         | information.                                                                                                                                                                                                                                                                               |

|             |                    | μ   | 0.0 V        | pinomaton.                                                                                                                                                                                                                                                                                 |

| J1A<br>Pin# | Signal Name   | I/O | Voltage  | Description                                                                                                                     |

|-------------|---------------|-----|----------|---------------------------------------------------------------------------------------------------------------------------------|

|             |               |     |          | IEEE1588 Real Time Clock input trigger to capture timestamps 2. See<br>Freescale's MPC8360E Processor Reference Manual for more |

| A49         | PTP EXT TRIG2 |     | 3.3V     | information.                                                                                                                    |

| 743         |               |     | 0.01     | TDM 0 transmit data sync. See Freescale's MPC8360E Processor                                                                    |

| A50         | TDM0 TSYNC    | 1   | 3.3V     | Reference Manual for more information.                                                                                          |

| A51         | GND           | 1   | GND      | Ground. Connect to digital ground.                                                                                              |

| A52         | TOUCH TOP     | İ   | max 3.3V | Touch panel TOP input signal.                                                                                                   |

| A53         | TOUCH_RIGHT   | 1   | max 3.3V | Touch panel RIGHT input signal.                                                                                                 |

| A54         | GPIO PA13     | I/O | 3.3V     | COM Express GPI0. Connected to GPI0_PA13 of the MPC8360.                                                                        |

| A55         | uP UART3 CTS  | 1   | 3.3V     | Clear To Send signal for UART3.                                                                                                 |

| A56         | uP UART3 RTS  | 0   | 3.3V     | Ready To Send signal for UART4.                                                                                                 |

| A57         | GND           | Ĩ   | GND      | Ground. Connect to digital ground.                                                                                              |

| A58         | uP UART4 CTS  | ĺ   | 3.3V     | Clear To Send signal for UART4.                                                                                                 |

| A59         | uP UART4 RTS  | 0   | 3.3V     | Ready To Send signal for UART4.                                                                                                 |

| A60         | GND           |     | GND      | Ground. Connect to digital ground.                                                                                              |

| / 100       |               |     | 0 ND     | TDM 0 clock out. See Freescale's MPC8360E Processor Reference                                                                   |

| A61         | TDM0 CLKO     | 0   | 3.3V     | Manual for more information.                                                                                                    |

|             |               | -   |          | TDM 0 IDL request permission to transmit on D channel. See                                                                      |

|             |               |     |          | Freescale's MPC8360E Processor Reference Manual for more                                                                        |

| A62         | TDM0 nRQ      | 0   | 3.3V     | information.                                                                                                                    |

| A63         | GPIO PB4      | I/O | 3.3V     | COM Express GPI1. Connected to GPIO PB4 of the MPC8360.                                                                         |

| A64         | NC            | NC  | NA       | Reserved for future use. Do not connect.                                                                                        |

| A65         | NC            | NC  | NA       | Reserved for future use. Do not connect.                                                                                        |

| A66         | GND           | I   | GND      | Ground. Connect to digital ground.                                                                                              |

| A67         | GPIO PA16     | I/O | 3.3V     | COM Express GPI2. Connected to GPIO PA16 of the MPC8360.                                                                        |

| A68         | NC            | NC  | NA       | Reserved for future use. Do not connect.                                                                                        |

| A69         | NC            | NC  | NA       | Reserved for future use. Do not connect.                                                                                        |

| A70         | GND           | 1   | GND      | Ground. Connect to digital ground.                                                                                              |

|             |               |     |          | Digital video group 0 LVDS out. Route as differential pair with                                                                 |

| A71         | LVDS A0+      | 0   | 3.3V     | LVDS_A0 Route pair with 100 ohms differntial impedance.                                                                         |

|             |               |     |          | Digital video group 0 LVDS out. Route as differential pair with                                                                 |

| A72         | LVDS_A0-      | 0   | 3.3V     | LVDS_A0+. Route pair with 100 ohms differntial impedance.                                                                       |

|             |               |     |          | Digital video group 1 LVDS out. Route as differential pair with                                                                 |

| A73         | LVDS_A1+      | 0   | 3.3V     | LVDS_A1 Route pair with 100 ohms differntial impedance.                                                                         |

|             |               |     |          | Digital video group 1 LVDS out. Route as differential pair with                                                                 |

| A74         | LVDS_A1-      | 0   | 3.3V     | LVDS_A1+. Route pair with 100 ohms differntial impedance.                                                                       |

|             |               |     |          | Digital video group 2 LVDS out. Route as differential pair with                                                                 |

| A75         | LVDS_A2+      | 0   | 3.3V     | LVDS_A2 Route pair with 100 ohms differntial impedance.                                                                         |

|             |               |     |          | Digital video group 2 LVDS out. Route as differential pair with                                                                 |

| A76         | LVDS_A2-      | 0   | 3.3V     | LVDS_A2+. Route pair with 100 ohms differntial impedance.                                                                       |

|             |               |     |          | LVDS VDD Enable. GPIO_PC22 of the MPC8360 is used to                                                                            |

| A77         | GPIO_PC22     | I/O | 3.3V     | enable/disable VDD for the LVDS interface.                                                                                      |

| . = 0       |               |     | o. o) (  | Digital video group 3 LVDS out. Route as differential pair with                                                                 |

| A78         | LVDS_A3+      | 0   | 3.3V     | LVDS_A3 Route pair with 100 ohms differntial impedance.                                                                         |

| . 70        |               |     | 0.01/    | Digital video group 3 LVDS out. Route as differential pair with                                                                 |

| A79         | LVDS_A3-      | 0   | 3.3V     | LVDS_A3+. Route pair with 100 ohms differntial impedance.                                                                       |

| A80         | GND           |     | GND      | Ground. Connect to digital ground.                                                                                              |

| 101         |               |     | 0.01/    | Digital video LVDS clock out. Route as differential pair with                                                                   |

| A81         | LVDS_A_CK+    | 0   | 3.3V     | LVDS_A_CK Route pair with 100 ohms differential impedance.                                                                      |

| 100         |               |     | 2 2)/    | Digital video LVDS clock out. Route as differential pair with                                                                   |

| A82         | LVDS_A_CK-    | 0   | 3.3V     | LVDS_A_CK+. Route pair with 100 ohms differntial impedance.                                                                     |

| 100         |               |     | 2 2)/    | I2C interface 2 clock signal. Pulled up to 3.3V_IO_VDD through a                                                                |

| A83         | I2C2_CLK      | I/O | 3.3V     | 2.2K resistor.                                                                                                                  |

| 101         |               |     | 2 21/    | I2C interface 2 data signal. Pulled up to 3.3V_IO_VDD through a 2.2K                                                            |

| A84         | I2C2_DATA     | 1/0 | 3.3V     | resistor.                                                                                                                       |

| A85         | GPIO_PA22     | I/O | 3.3V     | COM Express GPI3. Connected to GPIO_PA22 of the MPC8360.                                                                        |

| J1A<br>Pin# | Signal Name | I/O | Voltage | Description                                                                      |

|-------------|-------------|-----|---------|----------------------------------------------------------------------------------|

| F111#       | Signal Name | 1/0 | voltage | Reserved for future use. Connected to GPIO PC24 of the MPC8360.                  |

| A86         | GPIO_PC24   | I/O | 3.3V    | See Note 1 at the bottom of this table.                                          |

| / 100       |             | 1/0 | 0.0 V   | Reserved for future use. Connected to GPIO PC25 of the MPC8360.                  |

| A87         | GPIO PC25   | I/O | 3.3V    | See Note 1 at the bottom of this table.                                          |

| A88         | NC          | NC  | NA      | Reserved for future use. Do not connect.                                         |

| A89         | NC          | NC  | NA      | Reserved for future use. Do not connect.                                         |

| A90         | GND         |     | GND     | Ground. Connect to digital ground.                                               |

| A91         | NC          | NC  | NA      | No connect. Do not connect.                                                      |

| A92         | NC          | NC  | NA      | No connect. Do not connect.                                                      |

| A93         | GPIO PB6    | I/O | 3.3V    | COM Express GPO0. Connected to GPIO_PB6 of the MPC8360.                          |

| A94         | NC          | NC  | NA      | No connect. Do not connect.                                                      |

| A95         | NC          | NC  | NA      | No connect. Do not connect.                                                      |

| A96         | GND         |     | GND     | Ground. Connect to digital ground.                                               |

|             |             |     | -       | External 12V power input. This signal supplies the power switchers on            |

| A97         | 12V         | I   | 12V     | the board.                                                                       |

|             |             |     |         | External 12V power input. This signal supplies the power switchers on            |

| A98         | 12V         | I   | 12V     | the board.                                                                       |

|             |             |     |         | External 12V power input. This signal supplies the power switchers on            |

| A99         | 12V         | I   | 12V     | the board.                                                                       |

| A100        | GND         | I   | GND     | Ground. Connect to digital ground.                                               |

|             |             |     |         | External 12V power input. This signal supplies the power switchers on            |

| A101        | 12V         |     | 12V     | the board.                                                                       |

|             |             |     |         | External 12V power input. This signal supplies the power switchers on            |

| A102        | 12V         |     | 12V     | the board.                                                                       |

|             |             | _   |         | External 12V power input. This signal supplies the power switchers on            |

| A103        | 12V         |     | 12V     | the board.                                                                       |

|             |             |     |         | External 12V power input. This signal supplies the power switchers on            |

| A104        | 12V         | I   | 12V     | the board.                                                                       |

| 4.405       | 40) /       |     | 10) (   | External 12V power input. This signal supplies the power switchers on            |

| A105        | 12V         | I   | 12V     | the board.                                                                       |

| 4400        | 40)/        |     | 10)/    | External 12V power input. This signal supplies the power switchers on            |

| A106        | 12V         |     | 12V     | the board.                                                                       |

| A 107       | 12V         |     | 12V     | External 12V power input. This signal supplies the power switchers on the board. |

| A107        | 1 Z V       | 1   | 120     | External 12V power input. This signal supplies the power switchers on            |

| A108        | 12V         |     | 12V     | the board.                                                                       |

| AIUO        | 1 Z V       | 1   | 120     | External 12V power input. This signal supplies the power switchers on            |

| A109        | 12V         |     | 12V     | the board.                                                                       |

| A109        | GND         | I   | GND     | Ground. Connect to digital ground.                                               |

| AIIU        |             | I   | GND     |                                                                                  |

#### 5.1.2 J1A Row B Pin Descriptions

| J1A  |              |     |         |                                            |