# **Multi-Card Engine Design**

White Paper 184

Andrew Wawra, Kurt Larson

Logic Product Development

Published: November 2003

# Abstract

An OEM's ability to use multiple card engines on the same base board allows for upgrades to more advanced products and/or different levels of functionality without changing the underlying hardware. Designing a base board for multiple card engines is called Multi-Card Engine Design. This white paper outlines common design practices, tools, and areas of concern to keep in mind when designing a base board for multiple card engines.

This file contains source code, ideas, techniques, and information (the Information) which are Proprietary and Confidential Information of Logic Product Development, Inc. This information may not be used by or disclosed to any third party except under written license, and shall be subject to the limitations prescribed under license.

No warranties of any nature are extended by this document. Any product and related material disclosed herein are only furnished pursuant and subject to the terms and conditions of a duly executed license or agreement to purchase or lease equipments. The only warranties made by Logic Product Development, if any, with respect to the products described in this document are set forth in such license or agreement. Logic Product Development cannot accept any financial or other responsibility that may be the result of your use of the information in this document or software material, including direct, indirect, special or consequential damages.

Logic Product Development may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering the subject matter in this document. Except as expressly provided in any written agreement from Logic Product Development, the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions.

© Copyright 2002, Logic Product Development, Inc. All Rights Reserved.

#### **REVISION HISTORY**

| REV | EDITOR       | DESCRIPTION                    | APPROVAL | DATE       |

|-----|--------------|--------------------------------|----------|------------|

| 1   | Andrew Wawra | Preliminary Version            | AW       | 05/2003    |

| A   | Kurt Larson  | Release                        | HAR      | 12/01/2003 |

| В   | James Wicks  | Card Engine Pin-out Chart Text | JAW      | 07/19/2004 |

### 1 Introduction

Multi-Card Engine design offers many advantages to OEM's developing products. This white paper explains these advantages in the following sections: Card Engine Concept, Card Engine Interface, and Card Engine Pin-Out Chart.

### 2 Card Engine Concept

Logic's card engines can greatly accelerate your product's time to market. In addition, the card engines provide the following advantages:

- Product Ready Hardware & Software solutions allow immediate application development which results in embedded product development cycle with less time, less cost, less risk, and more innovation.

- Less time time to market solution allows software application development to begin immediately

- □ Less cost significantly lowers development cost

- □ Less risk complex portion of design product ready

- More Innovation Allows you to focus on your IP

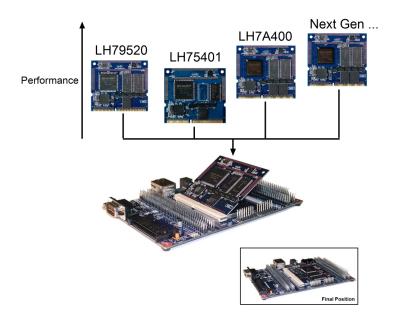

- Common Card Engine Footprint (See Figure 1)

- Easy migration path to new processors and technology

- Provides a scaleable solution for your product family

- □ Extends product life cycle worry free component obsolescence

- Low Cost Hardware Solution Custom configurations to meet your design requirements and price points.

- Complex portion of the design complete and ready to go.

#### Figure 1: Card Engine Advantages

Encapsulating a significant amount of your design onto the card engine reduces risk of obsolescence issues. If a component on the card engine design becomes obsolete you don't have to re-spin your board, Logic will design for alternative part that is transparent to your product. Manufacturing also becomes much easier. Card engines are delivered to you fully tested, making your manufacturing process simpler and less costly.

## 3 Card Engine Interface

The card engine's common interface allows you to easily migrate to new processors and technology. By using the common footprint, you can leverage Logic's work without having to respin your product.

The card engine interface is based on a 144-SODIMM connector and two 80 pin high density connectors. These connectors have generic signal designations across all card engine designs.

The signals from the 144-SODIMM connector contain the essential power and ground signals required to operate the card engine and the main host interface connection signals. The 144-SODIMM connector designated J1C contains the address, data, interrupt, host bus, Ethernet, SPI, Mode, and UARTA signals.

Expansion connector J1A contains the LCD, AC97, USB, AUDIO, Touch, Sense, and ADC signals.

Expansion connector J1B contains PCMCIA, IR, UARTB, UARTC, and Multi Function Pins. (MFP's) MFP's allow each card engine to use the variety of peripherals each processor supports, and are usually the area of greatest concern in multi-card engine design.

#### 3.1 144-SODIMM Signals

#### 3.1.1 Data Bus

The SODIMM connector has 32 pins dedicated for card engine data bus signals. Depending on the specific card engine chosen, the processor could have a 16 bit, 32 bit, or 64 bit internal data bus.

If the processor has a bus larger than 32 bits, only the lower 32 bits of the data bus will be provided external to the card engine. If the processor has 32 data bits or less, the entire data bus is provided off the card engine.

The data signal location, for a bus less than 32 bits, aligns at the locations of the lower bits of the 32 dedicated data signals on the card engine. For example, the LH75401 card engine has a 16 bit data bus. The processor data signals D0 to D15 are connected directly to the LH75401 card engine 144-SODIMM connector locations D0-D15. D16-D31 are *not connected* on the LH75401 card engine.

All 32 data signals are buffered on the card engine.

#### 3.1.2 Address Bus

The SODIMM connector has dedicated locations for up to 28 address lines. Some card engines utilize processors that support less than all 28 address lines.

The Integrated Development Kit (IDK) reference design includes a CPLD that has memory mapped registers which utilize A25 down to A20 for address decoding. To allow the address decoding across all card engines on the IDK and similar designs, card engines based on processors with less that 25 address lines (e.g. LH75401-based card engines) shift their high order address lines up to fill the A25 down to A20 slots.

It is important to refer to the documentation for each specific card engine before a design begins to understand the routing of address lines A25-A20 on the SODIMM connector.

#### 3.1.3 Ethernet Controller

Currently all card engines support an onboard 10/100 Ethernet controller. The Ethernet signals on the SODIMM connector have dedicated locations for TX and RX pairs, an nLINK, and nACT LED signals. Follow the Starter Development Kit (SDK) or IDK reference designs for proper connector interfacing including required impedance matching circuitry.

#### 3.1.4 SPI

The availability of the SODIMM dedicated SPI interface is dependent on the availability of the SPI supported by the processor.

Some processors support multiple serial interfaces in which the superset is called a Synchronous Serial Port (SSP); these processors include compatibility with the following formats: Motorola SPI, National Semiconductor MICROWIRE, and Texas Instruments Synchronous Serial Interfaces.

Not all card engines support the full SSP - it depends on the on the product selected. Please refer to the documentation on the specific card engine to determine whether or not it will support the synchronous serial mode required by the design.

#### 3.1.5 Dedicated Interrupts

The dedicated interrupt signals includes four interrupts (uP\_nIRQA through uP\_nIRQD), and in some cases an additional Non-Maskable Interrupt (nNMI) on the card engine SODIMM interface. Logic attempts to provide four separate interrupts and an nNMI signal for all processors.

In some cases the processor does not support dedicated external interrupts for all four IRQ signals. In those cases, either the onboard CPLD multiplexes multiple external card engine interrupts to a single interrupt that returns to the processor or an interruptable GPIO pin may be used.

Some interrupt signals require a specific level or edge signal to create the interrupt condition. For example, one card engine may require a low level interrupt condition on uP\_IRQD, while another will require a falling edge. Please consult the specific card engine documentation.

To design for the greatest degree of compatibility, use the lowest order interrupts first. For example, use uP\_nIRQA before using uP\_nIRQB.

#### 3.1.6 Mode Pins

The SODIMM has 4 mode pins on every card engine.

To design for multiple card engine compatibility, leave the Mode signals unconnected on the base board if the default software and hardware configuration used on the card engine. If your product requires an external boot device or an Endian setting change, ensure that all the card engines you are designing for support the settings desired.

Mode pins 0 and 1 are used to select the width of the boot device. Mode 0 and Mode 1 have pull ups and pull downs on the card engine to automatically boot from onboard flash.

One item that can easily cause problems is an external boot source. If an external boot source is used, you may have to change Mode pins 0 and 1 for the boot device. If two different card engines are designed in, their Mode 0 and Mode 1 settings may require different pull up or pull down requirements to correctly setup the boot width of the external device. To design for multiple card engines, design the product so that the Mode 0 and Mode 1 pins can be tied to ground or to 3.3V by a different configuration resistor population / build of material configuration.

For prototype designs it may be desirable to put down a strong pull up and a dip switch to ground for ease of configuring these Mode pins. Refer to the IDK design for an implementation of multiple Mode pin settings.

Mode pin 2 selects little or big endian memory architecture and has a pull up on the card engine. Not all card engines support little or big endian selection. Logic's standard is to implement little endian architecture by default.

Mode pin 3 selects on-board or off-board boot device selection. The on-board CPLD reads uP\_MODE3 to determine whether to assert the onboard flash chip select FLASH\_nCS or the external BOOT\_nCS signal. There is a pull-up on the uP\_MODE3 signal on the card engine so the device will boot from onboard flash.

#### 3.1.7 Power-on Reset State

Some signals are read by the card engine processor at the end of a power-on reset cycle to define the state of the processor at power-on reset.

Two signals defined on the SODIMM connector that set the processor state upon power-on reset are uP\_TEST1 and uP\_TEST2. The TEST1 and TEST2 signals are tied directly to the processor and their state at power on reset determines if the processor runs in Normal operation or JTAG/Test mode.

All card engines includes pull-ups on the board to put every processor in Normal operation mode. It is possible to override these signals with jumpers to ground or power on a baseboard to put the processors in JTAG/Test mode. If your design will include a JTAG interface that will be used for development, the uP\_TEST1 and uP\_TEST2 signals should be connected to configurable jumpers that allow for tying the signal directly to 3.3V power or ground.

Each processor will have a different defined state for the TEST1 and TEST2 pins determining Normal operation and JTAG/Test modes. It is important to have a configuration jumper available for each card engine that will be used on the baseboard. Refer to the SDK or IDK kit documentation for further information on JTAG jumper settings for various card engines and example designs for configuration jumper versatility.

#### 3.1.8 UARTA

The SODIMM connector has a dedicated location for a single UART designated UARTA. UARTA is setup as the debug serial port in Logic software offerings.

The UARTA peripheral has interface support for TX, RX, CTS, RTS, DTR, and DSR hardware signals. However, not every processor supports CTS, RTS, DTR, and DSR UART signals. If these signals are required for your product application, ensure that the card engines you choose to design for have the required control signals on the UARTA port.

The UARTA peripheral should be used as a dedicated manufacturing, field, and debug support serial port.

#### 3.1.9 Local Bus Control

The processor local bus control signals reside at designated locations on the SODIMM connector. Some of the supported signals are nWR, nRD, nCAS, nRAS, nBREQ, nBACK, nWAIT, DREQ, DRAK, DACK, nWE0, nWE1, nWE2, and nWE3. Each of these signals can be used to implement asynchronous or synchronous components on the bus.

From a control signal perspective, not all card engines support external wait states (nWAIT), bus requests(nBREQ, nBACK), or DMA requests (DREQ, DRAK, DACK). Each card engine's

documentation should be consulted before implementing to parts that require asserting external wait states, bus requests, or DMA requests.

There are also four available external memory chip selects for expanded base board devices: FAST\_nMCS, SLOW\_nMCS, VIDEO\_nMCS and BOOT\_nMCS. These chip selects are activated when designated areas of the processor's memory are accessed. For example, every card engine's on-board CPLD will have internal registers accessible in the designated FAST\_nMCS area. Please consult the individual card engine's hardware specification documents for the specific memory map and usage information on these chip select signals.

#### 3.1.10 Clocks

The SODIMM connector has two clock signals: uP\_BUS\_CLK and uP\_AUX\_CLK. On most card engines, these signals are derived from the processor's bus clock.

The uP\_BUS\_CLK is the clock used on the card engine to clock in bus transactions to the onboard SDRAM and CPLD. uP\_AUX\_CLK comes from the processor, but is not used on the card engine.

The frequency of uP\_BUS\_CLK is different for each card engine. The uP\_AUX\_CLK is controlled in the processor and in some cases has internal dividers and multipliers to get desired output frequencies.

The uP\_AUX\_CLK signal should be the primary clock used on the base board for bus synchronization. The use of uP\_BUS\_CLK is discouraged on a baseboard design except as a debugging reference.

When designing for multiple card engine compatibility, note that the uP\_BUS\_CLK and uP\_AUX\_CLK frequencies may be different for each card engine.

#### 3.1.11 JTAG

The card engine SODIMM connector has a JTAG interface that consists of TMS, TDO, TDI, TCK, and nTRST signals.

Most processors implement all of these signals for a test/debug JTAG interface. In some cases a processor may have additional test signals required for example RTCK on ARM7 processors. The RTCK signal and any other JTAG signals not included in the above list can be found on the J1B expansion connector on processors that require those signals for proper JTAG operation.

Another item to consider is that different processors may have different JTAG debug devices. The different devices may require different connectors on the baseboard. To save space and cost, designers may opt to put a single connector down that has all available JTAG signals and create different custom cables to connect to each processor specific JTAG device.

#### 3.2 80 pin Expansion Connector J1A Signals

#### 3.2.1 Voltage Sense Resistors

The 80 pin expansion connector J1A has 2 signals designated for a voltage sense resistor on the card engine: POWER\_SENSE1 and POWER\_SENSE2.

The sense resistor is used as part of a feedback network on the SDK and IDK development kits to determine the required VCORE voltage to supply to the card engine.

Refer to the SDK kit documentation for an example circuit showing a LDO voltage regulator or the IDK kit documentation for an example of a switching supply circuit to create VCORE dynamically for each card engine.

Using the onboard sense resistor, a single VCORE voltage supply design is possible. If the onboard sense resistor is not used, the voltage supply must be able to change the VCORE voltage from 1.4V to 2V depending on the card engines to be used in the product.

Correct implementation of a core voltage control by using these signals or some other mechanism is absolutely essential for successful multi-card engine design.

#### 3.2.2 USB

The J1A expansion connecter holds the 2 dedicated USB signal sets. The USB signals are generically named uP\_USBx\_M, uP\_USBx\_P, uP\_USBx\_nOVR\_CRNT, and uP\_USBx\_PWR\_EN. Where x is either 1 or 2. Not all processors have USB support.

When a processor supports USB function/client/device the data signals are connected to the uP\_USB1 positions on the J1A expansion connector.

The uP\_USB2 J1A expansion connector is used for USB host interface connections.

Some processors have USB client and host interfaces muxed on the same signals which is software selectable. For USB peripherals that have muxed client/host interfaces they muxed USB connection is connected to the up\_USB1 signal set.

For processors that support two host and no client connections, the uP\_USB1 and uP\_USB2 signal sets are used-- one for each host interface.

For processors that support two host and one client connections, uP\_USB1 is used for the single client interface, uP\_USB2 is used for one host interface, and the second host interface is connected to available MFP pins.

To design a multi-card engine product that utilizes the card engine USB connections, ensure that all card engines intended to be used in the design support the desired USB host/client interfaces.

#### 3.2.3 ADC and DAC

The J1A expansion connector has 4 signals that may support multiple Analog to Digital Converter (ADC) or Digtal to Analog Converter (DAC) signals if the card engine specific processor supports either of these devices.

Some devices may have two ADC's made available from an onboard Touch Screen Controller. Care must be taken to choose multiple card engines that support the desired functionality if ADC's or DAC's are required for the base board design.

#### 3.2.4 Analog Touch

The 4 wire analog touch signals reside on the J1A expansion connector. Depending on the processor, these signals are both driven and sensed by a stand alone touch screen controller IC or are controlled and sensed directly by the processor.

From a software perspective, if using any of Logic's BSPs, the touch software is a seamless interface between card engine products.

Some card engine product processors support a 5 wire touch interface. If your application requires 5 wire touch functionality, the  $5^{th}$  wire in the touch system is made available through the MFP pins on expansion connector J1B. When considering a 5 wire touch design, ensure that all desired card engine products support a 5 wire touch interface before attempting to design the base board.

#### 3.2.5 Audio Out

The card engine CODEC right and left inputs and outputs are available from the J1A expansion connector.

These signals are line level inputs/outputs; however, exact line level voltages may vary between card engine products based on the CODEC used on different card engines.

#### 3.2.6 LCD

Each card engine has a dedicated LCD interface. Each processor supports multiple types of LCD types including Color/Monochrome, STN, DSTN, TFT, HR-TFT, and others.

If the card engine LCD peripheral is required to support a specific display or multiple displays, it is important to verify that each card engine that will be used in the final product can support the desired LCD display.

Each processor may support a different number of LCD resolution bits, the card engine standard supports a 5-6-5 R-G-B format. The LCD connector has been pinned out so that a less than 18bit data bus can still drive all the bits of an 18 bit display.

The processor speed, LCD bandwidth, screen size, and color depth will all affect the LCD performance.

#### 3.2.7 Status Pins

The uP\_STATUS\_1, uP\_STATUS\_2, and CPLD\_GPIO\_1 signals are available on the J1A expansion connector and are used by Logic BSP's to indicate the device is operating.

Most baseboard designs should connect these signals to LED's that are connected through a resistor to a power rail.

Some processors allow the status signals to be used as general purpose I/O pins which can be reconfigured in customer specific software applications. Not all processors support this functionality, and in some cases the processor's status pins only indicate the current operating state of the processor.

#### 3.2.8 AC97 and I2S CODEC

The card engine interface has dedicated pins for an AC97 CODEC interface.

Most processors only have a single AC97 interface, so it is used to drive the onboard CODEC. The AC97 signals are made available on the J1A expansion connector for flexibility in CODEC

selection. The customer can opt to not have the card engine CODEC populated and use their own CODEC on their baseboard driven by the processor's AC97 link.

Some processors have duplicate AC97 interfaces; in these cases the first AC97 link is used for the onboard CODEC and the second link is provided at the J1A expansion connector.

I2S interfaces are sometimes muxed with the processor's AC97 link and can be used by the customer through the AC97 dedicated card engine interface.

In the case of an I2S interface, the SD\_IN is connected to the DATAOUT of the baseboard I2S CODEC and the SD\_OUT is connected to the DATAIN of the baseboard I2S CODEC. For a baseboard AC97 CODEC, SD\_OUT is connected to the CODEC DATAOUT pin; the SD\_IN is connected to the CODEC DATAIN pin.

#### 3.3 80 pin Expansion Connector J1B Signals

#### 3.3.1 UARTB and UARTC

The 80 pin expansion connector J1B has the dedicated locations for UARTB and UARTC serial ports.

UARTB and UARTC typically are processor specific serial ports and are generally available on all processors that support three serial ports.

In some cases, there are other peripheral chips on the card engine that have serial ports that can be used as UART's. The card engine may have one of these extra serial devices at a UARTB or UARTC location if the processor does not support multiple serial ports.

Please note that the UART flow control signal implementations may vary between card engine implementations.

#### 3.3.2 Infra-Red Serial Port

The J1B expansion connector also has two pins dedicated to an Infra Red serial port.

Most processors support IR ports and in some cases the IR port may be muxed with a UART. In muxed serial port cases, UARTB/C is mutually exclusive with the IR port.

For base boards that implement IR devices, ensure that all processors that will be used in the product support IR before relying on the IR port of a single product.

#### 3.3.3 PCMCIA

The J1B expansion connector has signals dedicated to the card engine PCMCIA interface.

The PCMCIA interface has multiple control signals for accessing different types of PC cards. For multi-card engine designs that will be using the PCMCIA/ PC Card interface, reference the IDK kit design documentation for an example design that implements a PCMCIA / PC Card interface that is compatible with all card engine PCMCIA / PC Card enabled products.

Before designing a product based around the card engine PCMCIA interface, ensure that the desired card engines that will be targeted for the end product have PCMCIA capability.

#### 3.3.4 Multi-Function Pins

The remaining signals on the J1B expansion connector are dedicated as Multi Function Pins or MFP's.

MFP's are signals that are not designated from a card engine level, but are based around the peripherals of the processor. The MFP signals allow Logic to maximize the feature sets of the chosen processor for a specific card engine. Different processors support different peripherals, and that is why Logic makes different card engines.

The MFP's are intelligently mapped out so that card engines with similar MFP peripherals line up exactly across multiple card engine products. This ensures that if two card engines support I2C interfaces, a customer can design a product with an I2C device and switch between the two different card engines and still be able to support the I2C device without changing any hardware.

The following is a list of some of the features that can be found on current card engine products: I2C, battery monitoring, additional serial ports, PWM signals, buzzer outputs, specific clock inputs, expanded chip selects, keypad interfaces, PS2 keyboard/mouse inputs, Smart Card Interfaces, MMC interfaces, additional LCD signals not defined in the dedicated LCD interface,

CPLD GPIO, additional CODEC inputs/outputs, additional external DMA signals, and additional USB host or client interfaces.

# 4 Card Engine Pin-Out Chart

The chart below presents a general card engine pin-out for Logic's card engines. *Please refer to respective card engine hardware specification, such as the "LH7A400-10 Card Engine Hardware Specification," for specific pin-out similarities and differences.*

| PIN #            | GROUP | SIGNAL NAME                 | MUX      | I/O    | Description                                                                                             |

|------------------|-------|-----------------------------|----------|--------|---------------------------------------------------------------------------------------------------------|

| J1A.01           | LCD   | LCD VSYNC                   |          | 0      | LCD Vsync/ Frame line marker (active state selectable)    General purpose I/O PTE3.                     |

|                  | LCD   | LCD_VSTINC                  |          | 0      | LCD vsync/ riane me marcel (active state selectable)    General purpose I/O PTD5.                       |

|                  |       | LCD DCLK                    |          | 0      | LCD data clock    General purpose I/O PTH7.                                                             |

|                  |       | LCD DON                     |          | 0      | Active high. LCD display on signal    General purpose I/O PTD7.                                         |

|                  |       | LCD MDISP                   |          | 0      | LCD current alternating signal/LCD enable signal    General purpose I/O PTE6.                           |

|                  |       | LCD_WIDISI                  |          | 0      | Active high. LCD panel Vee enable.                                                                      |

|                  |       | LCD_VELEN                   |          | 0      | Active high. LCD panel Vcc enable.                                                                      |

|                  | LCD   | LCD_VDDEN<br>LCD_CLK_RETURN |          | 1      | LCD clock input signal                                                                                  |

| J1A.08           |       | DGND                        |          | 1      | Digital Ground (0V)                                                                                     |

| J1A.09           | PWR   |                             |          | 1      |                                                                                                         |

|                  | LCD   | LCD_CLS                     |          | 0      | LCD signal                                                                                              |

|                  |       | LCD_SPS                     |          | 0      | LCD signal                                                                                              |

|                  |       | LCD_PSAVE                   |          | 0      | LCD signal                                                                                              |

|                  |       | LCD_SPL                     |          | 0      | LCD signal                                                                                              |

|                  |       | LCD_HRLP                    |          | 0      | LCD signal                                                                                              |

|                  |       | LCD_MOD                     |          | 0      | LCD signal                                                                                              |

|                  | LCD   | LCD_REV                     |          | 0      | LCD signal                                                                                              |

| J1A.17           |       | uP_STATUS_1                 |          | 0      | Processor status pin. uP_STATUS_2/uP_STATUS_1 -> 0/0 = Running, 0/1= Standby, 1/0 = Sleep,              |

|                  |       | uP_STATUS_2                 |          | 0      | Processor status pin. uP_STATUS_2/uP_STATUS_1 -> 0/0 = Running, 0/1 = Standby, 1/0 = Sleep,             |

| J1A.19           | CODEC | uP_AC97_BITCLK0             |          | 0      | AC97 Clock signal                                                                                       |

| J1A.20           | CODEC | uP_AC97_nRESET              |          | I      | Active Low. AC97 reset signal                                                                           |

| J1A.21           | CODEC | uP_AC97_SYNC0               |          | 0      | AC97 signal                                                                                             |

| J1A.22           | CODEC | uP_AC97_SD_IN0              |          | I      | AC97 signal                                                                                             |

|                  |       | uP_AC97_SD_OUT0             |          | 0      | AC97 signal                                                                                             |

| J1A.24           | PWR   | DGND                        |          | I      | Digital Ground (0V)                                                                                     |

|                  | AFE   | A/D1                        |          | I      | Analog input (pin ANx) : 0 to 3.3V swing possible.                                                      |

| J1A.26           | AFE   | A/D2                        |          | I      | Analog input (pin AN4) : 0 to 3.3V swing possible.                                                      |

| J1A.27           | PWR   | AGND                        |          | I      | Analog Ground (0V)                                                                                      |

|                  | MFP   | MFP39 (A/D4 - HP OUTL)      | Y        | I    O | Analog input (pin AN7) : 0 to 3.3V swing possible    Analog output (SH7727 pin DA0)                     |

| J1A.29           | MFP   | MFP40 (A/D4 - HP_OUTL)      |          | I/O    | MFP bit 40                                                                                              |

| J1A.30           | PWR   | 3.3VA                       |          | I      | Analog Power Supply (3.3V)                                                                              |

| J1A.31           | CODEC | CODEC INL                   |          | I      | Left channel stereo line-in input of the audio CODEC. 1V RMS typcial, 2V RMS max (if current            |

| J1A.32           |       | CODEC INR                   |          | I      | Right channel stereo line-in input of the audio CODEC. 1V RMS typeial, 2V RMS max (if current           |

|                  |       | CODEC OUTL                  |          | 0      | Left stereo mixer-channel line output. Nominal output level is 1.0 Vrms.                                |

| J1A.34           |       | CODEC OUTR                  |          | 0      | Right stereo mixer-channel line output. Nominal output level is 1.0 Vrms.                               |

|                  | PWR   |                             |          | 1      |                                                                                                         |

| J1A.35<br>J1A.36 |       | AGND<br>TOUCH LEFT          |          | 1      | Analog Ground (0V)<br>Four wire resistive touch X+ position connection.(LEFT)                           |

|                  |       | TOUCH_LEFT                  |          | 1      |                                                                                                         |

| J1A.37           |       |                             |          | 1      | Four wire resistive touch X- position connection. (RIGHT)                                               |

| J1A.38           |       | TOUCH_BOTTOM                |          | 1      | Four wire resistive touch Y- position connection.(BOTTOM)                                               |

| J1A.39           |       | TOUCH_TOP                   |          | 1      | Four wire resistive touch Y+ position connection. (TOP)                                                 |

|                  |       | 3.3VA                       |          | 1      | Analog Power Supply (3.3V)                                                                              |

| J1A.41           | LCD   | R0                          |          | 0      | The LCD data bus used to transmit data to the LCD module. RED 0 - internally shorted to R5 due to       |

| J1A.42           | LCD   | R1                          |          | 0      | The LCD data bus used to transmit data to the LCD module. RED 1                                         |

| J1A.43           | LCD   | R2                          |          | 0      | The LCD data bus used to transmit data to the LCD module. RED 2.                                        |

| J1A.44           | PWR   | DGND                        |          | I      | Digital Ground (0V)                                                                                     |

| J1A.45           | LCD   | R3                          |          | 0      | The LCD data bus used to transmit data to the LCD module. RED 3.                                        |

| J1A.46           | LCD   | R4                          |          | 0      | The LCD data bus used to transmit data to the LCD module. RED 4.                                        |

| J1A.47           | LCD   | R5                          |          | 0      | The LCD data bus used to transmit data to the LCD module. RED 5.                                        |

| J1A.48           | LCD   | G0                          |          | 0      | The LCD data bus used to transmit data to the LCD module. GREEN 0                                       |

| J1A.49           | LCD   | G1                          |          | 0      | The LCD data bus used to transmit data to the LCD module. GREEN 1.                                      |

| J1A.50           | LCD   | G2                          |          | 0      | The LCD data bus used to transmit data to the LCD module. GREEN 2.                                      |

|                  | LCD   | G3                          |          | 0      | The LCD data bus used to transmit data to the LCD module. GREEN 3.                                      |

| J1A.52           | LCD   | G4                          |          | 0      | The LCD data bus used to transmit data to the LCD module. GREEN 4                                       |

|                  |       | G5                          |          | 0      | The LCD data bus used to transmit data to the LCD module. GREEN 5                                       |

| J1A.54           | LCD   | B0                          |          | 0      | The LCD data bus used to transmit data to the LCD module. BLUE 0 - internally shorted to B5 due to      |

| J1A.54           | PWR   | DGND                        |          | Ĭ      | Digital Ground (0V)                                                                                     |

| J1A.56           | LCD   | B1                          |          | 0      | The LCD data bus used to transmit data to the LCD module. BLUE 1.                                       |

| J1A.57           |       | B2                          |          | 0      | The LCD data bus used to transmit data to the LCD module. BLUE 2.                                       |

| J1A.57<br>J1A.58 |       | B2<br>B3                    |          | 0      | The LCD data bus used to transmit data to the LCD module. BLUE 2.                                       |

| J1A.58<br>J1A.59 | LCD   | B4                          |          | 0      | The LCD data bus used to transmit data to the LCD module. BLUE 3.                                       |

|                  |       | B5                          |          | 0      | The LCD data bus used to transmit data to the LCD module. BLUE 4.                                       |

| J1A.60           | CF    | CF nCE                      |          | 0      | Active low. This signal is the chip/card select for the memory-only CF card. It indicates a word        |

|                  |       | RSVD 1                      |          | 0      | receive row. This signal is the emploard select for the memory-only Cr card. It indicates a word        |

| J1A.62           |       |                             | <b>├</b> | L/O    | This simplify a second summer 1/0 It is controlled to the last of the COV D                             |

|                  |       | CPLD_GPIO_1                 |          | I/O    | This signal is a general purpose I/O. It is controlled by a memory mapped address in the CPLD.          |

|                  | GPIO  | CPLD_GPIO_2                 |          | 1/0    | This signal is a general purpose I/O. It is controlled by a memory mapped address in the CPLD.          |

|                  | USB   | uP_USB2_nOVR_CRNT           |          | 1      | Active low. Signals an overcurrent condition on USB host port #2.                                       |

|                  |       | DGND                        |          | 1      | Digital Ground (0V)                                                                                     |

| J1A.67           | USB   | uP_USB1_nOVR_CRNT           |          | 1      | Active low. Signals an overcurrent condition when USB port #1 is configured as host. Signals cable      |

| J1A.68           | USB   | uP_USB2_PWR_EN              |          | 0      | Active high. Enables power supply for USB host port #2.                                                 |

|                  |       | uP_USB1_PWR_EN              |          | 0      | Active high. Enables power supply when USB port #1 is configured as host. Enables D+ pullup (TX         |

|                  | USB   | uP_USB2_M                   |          | I/O    | USB port #2 data I/O minus. Route as differential pair with uP_USB2_P.                                  |

| J1A.71           | USB   | uP_USB2_P                   |          | I/O    | USB port #2 data I/O plus. Route as differential pair with uP_USB2_M.                                   |

|                  | USB   | uP_USB1_M                   |          | I/O    | USB port #1 data I/O minus. Route as differential pair with uP_USB1_P.                                  |

|                  | USB   | uP_USB1_P                   |          | I/O    | USB port #1 data I/O plus. Route as differential pair with uP_USB1_M.                                   |

|                  |       | BUFF_nOE                    |          | I/O    | Active low. Controls the outputs of the buffers on the card engine. When low, the buffers are active,   |

|                  |       | BUFF_DIR_ADDRESS            |          | 0      | Active high/low. Controls the direction of the address lines through the buffers. When low, the         |

| J1A.76           | BUS   | BUFF_DIR_DATA               |          | I/O    | Active high/low. Controls the direction of the data lines through the buffers. When low, the data lines |

|                  |       | DGND                        |          | I      | Digital Ground (0V)                                                                                     |

|                  |       | MIC_IN                      |          | I      | Microphone input                                                                                        |

| J1A.79           |       | POWER_SENSE1                |          | I      | These two pins are used to set the core voltage of the card engine. For use with Logic Application      |

|                  |       | POWER SENSE2                |          | I      | These two pins are used to set the core voltage of the card engine. For use with Logic Application      |

| -                |       |                             |          |        |                                                                                                         |

| J1B.01                                                                       | DEBUG                                                | CPLD TCK                                                   | I      | I                                           | This is the test clock input for the CPLD JTAG port.                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------|--------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1B.02                                                                       | DEBUG                                                | CPLD_TDO                                                   |        | 0                                           | This input transmits data out of the CPLD JTAG port.                                                                                                                                                                                                                   |

| J1B.03                                                                       |                                                      | CPLD_TMS                                                   |        | 0                                           | This input indicates the mode of CPLD JTAG port.                                                                                                                                                                                                                       |

|                                                                              |                                                      | CPLD_TDI                                                   |        | I                                           | This input receives data on the CPLD JTAB port.                                                                                                                                                                                                                        |

| J1B.05                                                                       |                                                      | uP_PCC_nOE                                                 | Y      | 0                                           | Active low. This bufferred signal is the read strobe that latches data output from external peripherals.                                                                                                                                                               |

| J1B.06                                                                       |                                                      | uP_PCC_nWE                                                 | Y      | 0                                           | Active low. Bufferred write enable for buffered data bus bits 15->8 - PCMCIA WE - DQM1                                                                                                                                                                                 |

|                                                                              |                                                      | uP_PCC_nIORD<br>uP_PCC_nIOWR                               | Y<br>Y | 0<br>0                                      | Active low. Buffered write enable for buffered data bus bits 23->16 - PCMCIA IORD - DQM2<br>Active low. Buffered write enable for buffered data bus bits 31->24 - PCMCIA IOWR - DQM3                                                                                   |

| J1B.08<br>J1B.09                                                             |                                                      | DGND                                                       | 1      | U<br>I                                      | Digital Ground (0V)                                                                                                                                                                                                                                                    |

| J1B.10                                                                       |                                                      | uP PCC RESET                                               | Y      | 0                                           | DMA channel 0 external request acknowledge (active state selectable)    Active high. PCMCIA reset.                                                                                                                                                                     |

|                                                                              |                                                      | uP_PCC_nCE1B                                               | 1      | 0                                           | Active low. Chip/card enable signal for PCMCIA area 6 accesses signifying data bits 07 are valid.                                                                                                                                                                      |

| J1B.12                                                                       |                                                      | uP PCC nCE2B                                               |        | 0                                           | Active low. Chip/card enable signal for PCMCIA area 6 accesses signifying data bits 158 are valid.                                                                                                                                                                     |

| J1B.13                                                                       |                                                      | uP PCC nIOIS16                                             |        | I                                           | Active low. PCMCIA IOIS16 signal. When low, specifies 16 bit IO card or write protected memory                                                                                                                                                                         |

|                                                                              |                                                      | uP PCC RDY                                                 |        | I                                           | Active high. PCMCIA RDY signal. PCMCIA/CF card will hold this signal low until ready to be                                                                                                                                                                             |

|                                                                              |                                                      | uP_PCC_nWAIT                                               |        | I                                           | Active low. PCMCIA WAIT signal. Has same effect of holding the current bus cycle that uP_WAIT#                                                                                                                                                                         |

| J1B.16                                                                       | PCMCIA                                               | uP_PCC_BVD2                                                |        | I                                           | PCMCIA BVD2 signal.                                                                                                                                                                                                                                                    |

| J1B.17                                                                       | PCMCIA                                               | uP_PCC_BVD1                                                |        | I                                           | PCMCIA BVD1 singal.                                                                                                                                                                                                                                                    |

| J1B.18                                                                       | PCMCIA                                               | uP_PCC_nCD2                                                |        | I                                           | Active low. PCMCIA CD2 signal. Signals that one side of the PCMCIA/CF card is connected.                                                                                                                                                                               |

|                                                                              |                                                      | uP_PCC_nCD1                                                |        | I                                           | Active low. PCMCIA CD1 signal. Signals that one side of the PCMCIA/CF card is connected.                                                                                                                                                                               |

| J1B.20                                                                       |                                                      | uP_PCC_nREG                                                |        | 0                                           | Active low. PCMCIA REG signal. When asserted, this signal specifies accesses to card attribute                                                                                                                                                                         |

| J1B.21                                                                       | PWR                                                  | DGND                                                       |        | I                                           | Digital Ground (0V)                                                                                                                                                                                                                                                    |

| J1B.22                                                                       |                                                      | uP_PCC_VS1                                                 |        | I                                           | PCMCIA VS1 signal. Voltage sense.                                                                                                                                                                                                                                      |

| J1B.23                                                                       |                                                      | uP_PCC_VS2                                                 | ¥7     | 1                                           | PCMCIA VS2 signal. Voltage sense.                                                                                                                                                                                                                                      |

|                                                                              |                                                      | uP_PCC_nDRV                                                | Y      | 0                                           | DMA channel 0 acknowledge (active state selectable)    Active low. PCMCIA drive enable (can use                                                                                                                                                                        |

|                                                                              |                                                      | uP_PCC_DIR<br>uP_pDOM3                                     | v      | 0                                           | PCMCIA Data Direction Active low Ruffared write anable for huffered data bus bits 31 >24 PCMCIA IOWR DOM3                                                                                                                                                              |

| J1B.26<br>J1B.27                                                             |                                                      | uP_nDQM3<br>uP_nDQM2                                       | Y<br>Y | 0                                           | Active low. Buffered write enable for buffered data bus bits 31->24 - PCMCIA IOWR - DQM3<br>Active low. Buffered write enable for buffered data bus bits 23->16 - PCMCIA IORD - DQM2                                                                                   |

| J1B.27<br>J1B.28                                                             |                                                      | uP_nDQM2<br>uP_nDQM1                                       | Y      | 0                                           | Active low. Bufferred write enable for buffered data bus bits 25->16 - PCMCIA IORD - DQM2<br>Active low. Bufferred write enable for buffered data bus bits 15->8 - PCMCIA WE - DQM1                                                                                    |

| J1B.28<br>J1B.29                                                             |                                                      | uP_nDQM1<br>uP_nDQM0                                       | Y      | 0                                           | Active low. Buffered write enable for buffered data bus bits 7->0 - DQM0 SDRAM signal from the                                                                                                                                                                         |

|                                                                              | IRDA                                                 | uP IRTX                                                    | 1      | 0                                           | IRDA Transmit data                                                                                                                                                                                                                                                     |

|                                                                              | IRDA                                                 | uP IRRX                                                    |        | I                                           | IRDA Praisin data                                                                                                                                                                                                                                                      |

| J1B.32                                                                       | PWR                                                  | DGND                                                       |        | I                                           | Digital Ground (0V)                                                                                                                                                                                                                                                    |

| J1B.33                                                                       | MFP                                                  | MFP1                                                       |        | I/O                                         | MFP bit 1                                                                                                                                                                                                                                                              |

| J1B.34                                                                       | MFP                                                  | MFP2                                                       |        | I/O                                         | MFP bit 2                                                                                                                                                                                                                                                              |

| J1B.35                                                                       | MFP                                                  | MFP3                                                       |        | I/O                                         | MFP bit 3                                                                                                                                                                                                                                                              |

| J1B.36                                                                       | MFP                                                  | MFP4                                                       |        | I/O                                         | MFP bit 4                                                                                                                                                                                                                                                              |

| J1B.37                                                                       | MFP                                                  | MFP5                                                       |        | I/O                                         | MFP bit 5                                                                                                                                                                                                                                                              |

| J1B.38                                                                       | MFP                                                  | MFP6                                                       |        | I/O                                         | MFP bit 6                                                                                                                                                                                                                                                              |

| J1B.39                                                                       | MFP                                                  | MFP7                                                       |        | I/O                                         | MFP bit 7                                                                                                                                                                                                                                                              |

| J1B.40                                                                       | MFP                                                  | MFP8                                                       |        | I/O                                         | MFP bit 8                                                                                                                                                                                                                                                              |

| J1B.41                                                                       | UART                                                 | uP_UARTB_TX                                                |        | 0                                           | UARTB Transmit data                                                                                                                                                                                                                                                    |

| J1B.42                                                                       | UART                                                 | uP_UARTB_RX                                                |        | I                                           | UARTB Receive data                                                                                                                                                                                                                                                     |

| J1B.43                                                                       | UART                                                 | uP_UARTB_CTS                                               |        | I                                           | UARTB Clear to Send                                                                                                                                                                                                                                                    |

| J1B.44                                                                       | PWR                                                  | DGND                                                       |        | I                                           | Digital Ground (0V)                                                                                                                                                                                                                                                    |

| J1B.45                                                                       | UART                                                 | uP_UARTB_DSR                                               |        | 0                                           | UARTB Data Set Ready                                                                                                                                                                                                                                                   |

| J1B.46                                                                       | UART                                                 | uP_UARTC_TX                                                |        | 0                                           | UARTC Transmit data                                                                                                                                                                                                                                                    |

| J1B.47                                                                       | UART                                                 | uP_UARTC_RX                                                |        | 1                                           | UARTC Receive data                                                                                                                                                                                                                                                     |

| J1B.48                                                                       | MFP                                                  | MFP9                                                       | Y      | 0                                           | MFP bit 9                                                                                                                                                                                                                                                              |

| J1B.49                                                                       | MFP<br>MFP                                           | MFP10                                                      | Y<br>Y | I<br>T                                      | MFP bit 10                                                                                                                                                                                                                                                             |

| J1B.50<br>J1B.51                                                             | MFP                                                  | MFP11<br>MFP12                                             | Y      | I<br>I    I                                 | MFP bit 11 MFP bit 12                                                                                                                                                                                                                                                  |

| J1B.51<br>J1B.52                                                             | MFP                                                  | MFP12<br>MFP13                                             | Y      | I I I                                       | MFP bit 12<br>MFP bit 13                                                                                                                                                                                                                                               |

| J1B.52<br>J1B.53                                                             | MFP                                                  | MFP14                                                      | Y      | 0                                           | MFP bit 14                                                                                                                                                                                                                                                             |

| J1B.55                                                                       | MFP                                                  | MFP15                                                      | Y      | 0                                           | MFP bit 15                                                                                                                                                                                                                                                             |

| J1B.56                                                                       | MFP                                                  | MFP16                                                      | Y      | I                                           | MFP bit 16                                                                                                                                                                                                                                                             |

| J1B.57                                                                       | MFP                                                  | MFP17                                                      |        | I/O                                         | MFP bit 17                                                                                                                                                                                                                                                             |

| J1B.58                                                                       | MFP                                                  | MFP18                                                      | Y      | 0                                           | SIOF serial transmit data. This signal is attached to the on-board CODEC, but may be used to                                                                                                                                                                           |

| J1B.59                                                                       | MFP                                                  | MFP19                                                      | Y      | I                                           | SIOF serial receive data. This signal is attached to the on-board CODEC, but may be used to                                                                                                                                                                            |

| J1B.60                                                                       | MFP                                                  | MFP20                                                      | Y      | I/O                                         | SIOF serial frame sync signal. This signal is output in master mode and input in slave mode. This                                                                                                                                                                      |

| J1B.61                                                                       | MFP                                                  | MFP21                                                      | Y      | I/O                                         | SIOF serial communications clock. This signal is output in master mode and input in slave mode.                                                                                                                                                                        |

| J1B.62                                                                       | MFP                                                  | MFP22                                                      | Y      | I/O                                         | This signal is the master CODEC clock frequency and is typically output from the card engine. If the                                                                                                                                                                   |

| J1B.63                                                                       | MFP                                                  | MFP23                                                      | Y      | O    I                                      | Active high. Signals that the output of the CODEC is within 1dB of the rails.    If the on-board                                                                                                                                                                       |

| J1B.65                                                                       | MFP                                                  | MFP25                                                      | Y      | I/O                                         | This signal is a general purpose I/O. It is controlled by a memory mapped address in the CPLD.                                                                                                                                                                         |

| J1B.66                                                                       | PWR                                                  | DGND                                                       |        | I<br>VO                                     | Digital Ground (0V)                                                                                                                                                                                                                                                    |

| J1B.67                                                                       |                                                      | MFP26                                                      | Y      | I/O                                         | This signal is a general purpose I/O. It is controlled by a memory mapped address in the CPLD.                                                                                                                                                                         |

| J1B.68                                                                       | MFP                                                  | MFP27                                                      | Y      | I/O                                         | This signal is a general purpose I/O. It is controlled by a memory mapped address in the CPLD.                                                                                                                                                                         |

| 11D (0                                                                       |                                                      | MFP28                                                      | Y      | I/O<br>I/O                                  | This signal is a general purpose I/O. It is controlled by a memory mapped address in the CPLD.<br>This signal is a general purpose I/O. It is controlled by a memory mapped address in the CPLD.                                                                       |

| J1B.69                                                                       | MFP                                                  | MED20                                                      | v      |                                             |                                                                                                                                                                                                                                                                        |

| J1B.70                                                                       | MFP                                                  | MFP29<br>MEP30                                             | Y      |                                             |                                                                                                                                                                                                                                                                        |

| J1B.70<br>J1B.71                                                             | MFP<br>MFP                                           | MFP30                                                      | Y      | I/O                                         | Active low. Chip/card enable signal for PCMCIA area 5 accesses signifying data bits 158 are valid.                                                                                                                                                                     |

| J1B.70<br>J1B.71<br>J1B.72                                                   | MFP<br>MFP<br>MFP                                    | MFP30<br>MFP31                                             |        | I/O<br>I/O                                  | Active low. Chip/card enable signal for PCMCIA area 5 accesses signifying data bits 15.8 are valid.<br>This signal is a general purpose I/O. It is controlled by a memory mapped address in the CPLD.                                                                  |

| J1B.70<br>J1B.71<br>J1B.72<br>J1B.73                                         | MFP<br>MFP<br>MFP<br>MFP                             | MFP30<br>MFP31<br>MFP32                                    | Y      | I/O<br>I/O<br>I/O                           | Active low. Chip/card enable signal for PCMCIA area 5 accesses signifying data bits 15.8 are valid.<br>This signal is a general purpose I/O. It is controlled by a memory mapped address in the CPLD.<br>MFP bit 32                                                    |

| J1B.70<br>J1B.71<br>J1B.72<br>J1B.73<br>J1B.74                               | MFP<br>MFP<br>MFP<br>MFP<br>MFP                      | MFP30<br>MFP31<br>MFP32<br>MFP33                           | Y      | I/O<br>I/O<br>I/O<br>I/O                    | Active low. Chip/card enable signal for PCMCIA area 5 accesses signifying data bits 158 are valid.<br>This signal is a general purpose I/O. It is controlled by a memory mapped address in the CPLD.<br>MFP bit 32<br>MFP bit 33                                       |