## **REVISION HISTORY**

| REV | EDITOR                         | REVISION DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CARD<br>ENGINE<br>REV | APPROVAL | DATE    |

|-----|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|---------|

| 1   | Erik Reynolds                  | Beta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                     | ER       | 5/28/04 |

| Α   | James Wicks                    | Removed Preliminary References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 201                   | ER       | 8/19/04 |

| В   | James Wicks                    | Updated Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | А                     | ER       | 1/13/05 |

| С   | James Wicks /<br>Mike Aanenson | Connector Pin Descriptions:  - J1A pin 6 LCD_VEEEN  - J1B pin 11 PCC_nCE1B  - J1B pin 12 PCC_nCE2B  - J1B pin 18 PCC_nCD2  - J1B pin 19 PCC_nCD1  J1C multiplex table, Section 5.5.1:  - Removed Pins 17 and 18  - Pin 23 uP_IRQD corrected to INT4, PF4  J1A multiplex table, Section 5.5.2:  - Pin 7 changed to pin 6 LCD_VEEEN  - Added Pins 17 and 18, uP_STATUS1 and uP_STATUS2  - Added Pin 62, uP_PCC_RDYA  J1B multiplex table, Section 5.5.3:  - Pin 13 uP_PCC_nIOIS16 corrected to PA2  - Pin 14 uP_PCC_RDYB corrected to PF7  - Pin 15 uP_PCC_nVAIT corrected Alternate Description  - Removed Pins 16, 17, 18, and 19  - Pin 47 uP_UARTC_RX pin number corrected.  -Revision History Table corrected. Rev A was for Card Engine Rev 201. Rev B was for Card Engine Rev A. | В                     | MAA      | 3/18/05 |

| D   | Chris Rempel                   | Updated Section 5: Pin Descriptions & Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | В                     | HAR      | 5/6/05  |

| REV | EDITOR       | REVISION DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SCHEMATIC<br>PN & REV | APPROVAL | DATE     |

|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|----------|

| Е   | Jed Anderson | <ul> <li>Revision History Table: Replaced "Card Engine Rev" category with "Schematic PN &amp; Rev"</li> <li>Removed Section 1.4 "Card Engine Advantages"</li> <li>Sections 1.6.1 and 1.6.1.1: Updated tables</li> <li>Section 1.6.1.1: Added power supply note</li> <li>Section 2.1.2: Updated LH7A404 MCU Block Diagram</li> <li>Section 2.7: Updated link to Intel website</li> <li>Section 5.1: Changed J1C pin #22 nCHRDY to Input</li> <li>Section 5.1: Fixed description of pin #26 uP_TEST2 signal for proper JTAG use</li> <li>Section 5.2: Corrected J1A pin #11 LCD_VSYNC – LCD_SPS description</li> <li>Section 6.1: Updated Hirose connector PN after previous PN was discontinued</li> <li>Section 6.1: Added Important note</li> <li>General formatting and grammatical changes throughout</li> </ul> | 80000258<br>Rev C     | MAA      | 05/04/07 |

| F   | Jed Anderson | Updated Product Brief     Sections 1.3, 2.13, & 3.5.2: Removed references to the Altera CPLD and added references to the Xilinx CPLD     Removed references to the IDK kit throughout     General formatting and grammatical changes throughout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 80000258<br>Rev C     | JCA      | 06/27/07 |

Please check www.logicpd.com for the latest revision of this hardware specification, product change notifications, and additional application notes.

This file contains source code, ideas, techniques, and information (the Information) which are Proprietary and Confidential Information of Logic Product Development, Inc. This information may not be used by or disclosed to any third party except under written license, and shall be subject to the limitations prescribed under license.

No warranties of any nature are extended by this document. Any product and related material disclosed herein are only furnished pursuant and subject to the terms and conditions of a duly executed license or agreement to purchase or lease equipments. The only warranties made by Logic Product Development, if any, with respect to the products described in this document are set forth in such license or agreement. Logic Product Development cannot accept any financial or other responsibility that may be the result of your use of the information in this document or software material, including direct, indirect, special or consequential damages.

Logic Product Development may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering the subject matter in this document. Except as expressly provided in any written agreement from Logic Product Development, the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions

© Copyright 2004–2007, Logic Product Development, Inc. All Rights Reserved.

# **Table of Contents**

| 1 | Introduction                                                 |    |

|---|--------------------------------------------------------------|----|

|   | 1.1 Product Brief                                            |    |

|   | 1.2 Acronyms                                                 | 9  |

|   | 1.3 Technical Specification                                  |    |

|   | 1.4 Card Engine Interface                                    | 10 |

|   | 1.5 LH7A404-11 Card Engine Block Diagram                     | 11 |

|   | 1.6 Electrical, Mechanical, and Environmental Specifications |    |

|   | 1.6.1 Absolute Maximum Ratings                               |    |

|   | 1.6.1.1 Recommended Operating Conditions                     |    |

| 2 |                                                              | 14 |

|   | 2.1 Microcontroller                                          |    |

|   | 2.1.1 LH7A404 Microcontroller                                |    |

|   | 2.1.2 LH7A404 Microcontroller Block Diagram                  |    |

|   | 2.2 Clocks                                                   |    |

|   | 2.3 Memory                                                   |    |

|   | 2.3.1 Synchronous DRAM                                       |    |

|   | 2.3.2 Direct Memory Access (DMA)                             |    |

|   | 2.3.3 NOR Flash                                              |    |

|   |                                                              |    |

|   | 2.3.4 NAND Flash                                             |    |

|   | 2.3.5 EPROM                                                  |    |

|   | 2.3.6 CompactFlash (memory-mapped mode only)                 |    |

|   | 2.4 Secure Digital (SD) and MultiMediaCard (MMC)             |    |

|   | 2.5 PCMCIA/CompactFlash (external)                           |    |

|   | 2.6 10/100 Ethernet Controller                               |    |

|   | 2.7 Audio CODEC                                              |    |

|   | 2.8 Video Interface                                          |    |

|   | 2.9 Serial Interface                                         |    |

|   | 2.9.1 UARTA                                                  |    |

|   | 2.9.2 UARTB                                                  |    |

|   | 2.9.3 UARTC                                                  |    |

|   | 2.9.4 SSP/SPI                                                |    |

|   | 2.10 Keyboard and Mouse Interface (KMI)                      | 20 |

|   | 2.11 USB Interface                                           | 20 |

|   | 2.12 ADC/Touch Interface                                     | 20 |

|   | 2.13 General Purpose I/O                                     | 20 |

|   | 2.14 CPLD                                                    | 21 |

|   | 2.15 Serial EEPROM Interface                                 | 21 |

|   | 2.16 Expansion/Feature Options                               | 21 |

| 3 | System Integration                                           |    |

|   | 3.1 Configuration                                            | 22 |

|   | 3.2 Resets                                                   |    |

|   | 3.2.1 Master Reset (Hard Reset)                              |    |

|   | 3.2.2 Soft Reset                                             |    |

|   | 3.3 Interrupts                                               |    |

|   | 3.4 JTAG Debugger Interface                                  |    |

|   | 3.5 Power Management                                         |    |

|   | 3.5.1 System Power Supplies                                  |    |

|   | 3.5.1.1 3.3V uP SDRAM                                        |    |

|   | 3.5.1.2 3.3V                                                 |    |

|   | 3.5.1.2 3.3VA                                                |    |

|   | 3.5.1.4 3.3V_WRLAN                                           |    |

|   |                                                              |    |

|   | 3.5.1.5 VCORE                                                |    |

|   | 3.5.2 System Power Management                                | ∠0 |

|   | 3.5.3    | Peripherals                                        |    |

|---|----------|----------------------------------------------------|----|

|   | 3.5.4    | Microcontroller                                    | 27 |

|   | 3.5.4.   |                                                    |    |

|   | 3.5.4.2  | 2 Standby Mode                                     | 28 |

|   | 3.5.4.3  | 3 Halt Mode                                        | 28 |

|   | 3.6 ESE  | O Considerations                                   | 28 |

| 4 | Memory   | ∕ & I/O Mapping                                    | 29 |

|   |          | RAM Memory Map                                     |    |

|   | 4.2 Exte | ernal Static Memory Map                            | 30 |

|   | 4.2.1    | Card Engine Static Memory Map Description          |    |

|   | 4.2.2    | Chip Select 6 (CS6)—CPLD Peripherals (slow timing) |    |

|   | 4.2.3    | Chip Select 5 (CS7)—CPLD Peripherals (fast timing) | 32 |

| 5 |          | criptions & Functions                              |    |

|   | 5.1 J1C  | Connector SODIMM 144-Pin Descriptions              | 33 |

|   |          | Expansion Connector Pin Descriptions               |    |

|   |          | Expansion Connector Pin Description                |    |

|   |          | Jumper Table                                       |    |

|   | 5.5 Mul  | tiplexed Signal Trade-Offs                         |    |

|   | 5.5.1    | J1C Connector SODIMM 144-Pin Multiplexing          |    |

|   | 5.5.2    | J1A Expansion Connector Pin Multiplexing           |    |

|   | 5.5.3    | J1B Expansion Connector Pin Multiplexing           |    |

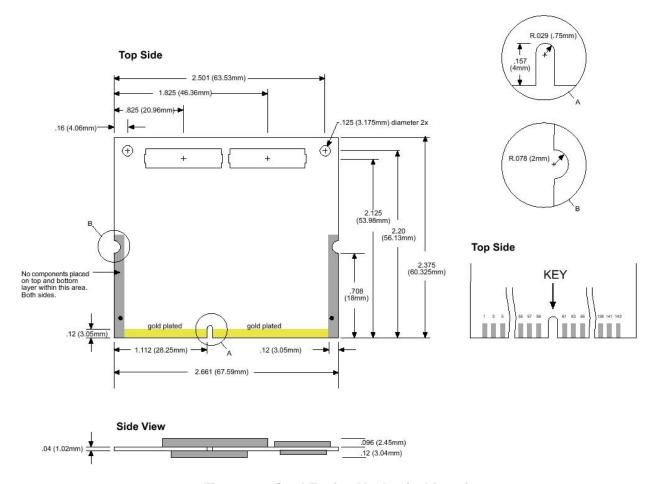

| 6 |          | ical Specifications                                |    |

|   | 6.1 Inte | rface Connectors                                   | 49 |

# **Table of Figures**

| Figure 1.1: Card Engine Advantages                |  |

|---------------------------------------------------|--|

| Figure 1.2: LH7A404-11 Card Engine Block Diagram  |  |

| Figure 2.1: LH7A404 Microcontroller Block Diagram |  |

| Figure 2.2: Serial EEPROM Block Diagram           |  |

| Figure 3.1: Reset Circuit                         |  |

| Figure 3.2: Soft Reset                            |  |

| Figure 3.3: Interrupt Priorities (high to low)    |  |

| Figure 3.4: Power Plane Diagram                   |  |

| Figure 4.1: LH7A404 SDRAM Memory Map              |  |

| Figure 4.2: LH7A404 Static Memory Map             |  |

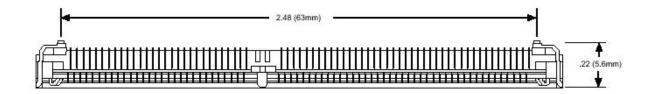

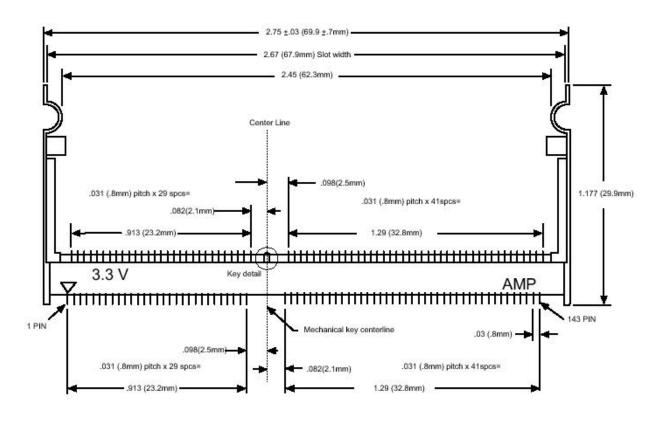

| Figure 6.1: Card Engine Mechanical Drawing        |  |

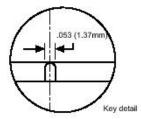

| Figure 6.2: SODIMM Connector Specification        |  |

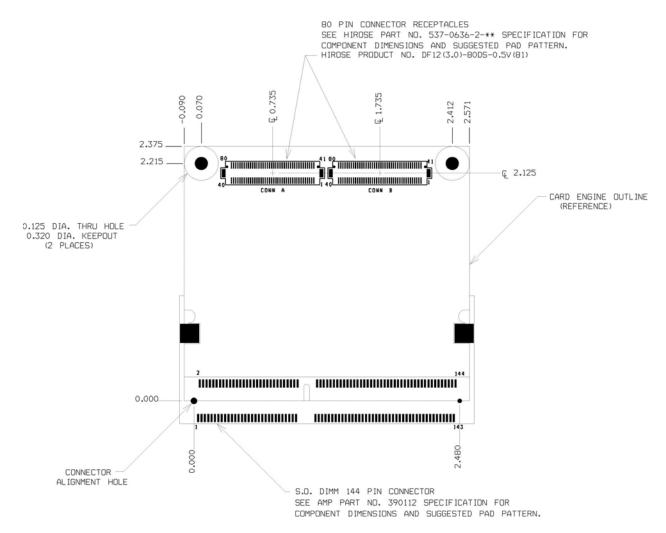

| Figure 6.3: Recommended PCB Layout                |  |

#### PRODUCT BRIEF:

Logic :: Sharp

# LH7A404 CARD ENGINE System on Module

The LH7A404 Card Engine is a compact, product-ready hardware and software solution that fast forwards your embedded product design.

The LH7A404 Card Engine is a complete System on Module (SOM) that offers essential features for handheld and embedded networking applications. Use of custom baseboards makes the Card Engine the ideal foundation for OEMs developing handheld and compact products. The Card Engine provides a common reference pin-out on its expansion connectors, which enables easy scalability to next generation microprocessor Card Engines when new functionality or performance is required.

Application development is performed right on the product-ready LH7A404 Card Engine and software Board Support Packages (BSPs), which enables you to seamlessly transfer your application code and hardware into production.

The LH7A404 Card Engine is ideal for applications in the medical, point-of-sale, industrial, and security markets. From patient

LH7A404 CARD ENGINE

monitoring and medical imaging, to card payment terminals and bar code readers, to CCTV cameras and intruder alarms, the LH7A404 Card Engine allows for powerful versatility and long-life products.

# LH7A404 CARD ENGINE :: HIGHLIGHTS:

- + Product-ready System on Module with the Sharp LH7A404 microprocessor running up to 200 MHz

- +Compact form factor 60.2 mm x 67.8 mm x 4.4 mm

- +Long product life-cycle

- +0 °C to 70 °C (commercial temp) or -40 °C to 85 °C (industrial temp)

- +RoHS compliant

# LH7A404 ZOOM™ SDK :: FEATURES:

- +Application baseboard

- +LH7A404 Card Engine (CENGLH7A404-11-503HCR)

- + Necessary accessories to immediately get up and running

- +Kit available from Logic (SDK-LH7A404-11-6416R)

- +See Zoom™ SDK product brief for more information

## LH7A404 Card Engine Block Diagram

# LH7A404 Card Engine Ordering Information

|                                   | Speed<br>(MHz) |    | NAND Flash<br>(MB) |    |   | Audio | Ethernet | Temp<br>(°C) |

|-----------------------------------|----------------|----|--------------------|----|---|-------|----------|--------------|

| CENGLH7A404-11-503HC <sup>1</sup> | 200            | 64 | 0                  | 16 | Υ | Υ     | Υ        | 0 – 70       |

| CENGLH7A404-11-503HCR             | 200            | 64 | 0                  | 16 | Υ | Υ     | Υ        | 0 – 70       |

| CENGLH7A404-11-504HCR             | 200            | 64 | 0                  | 32 | Υ | Υ     | Υ        | 0 – 70       |

| CENGLH7A404-11-504HIR             | 200            | 64 | 0                  | 32 | Υ | Υ     | Υ        | -40 – 85     |

<sup>1.</sup> This non-RoHS configuration is only available as part of the LH7A404 Zoom SDK. For production volumes, please use the RoHS compliant configuration.

# LH7A404 ZOOM™ SDK Ordering Information

| Logic Model Number               | SOM Configuration                 | Recommended Resale |

|----------------------------------|-----------------------------------|--------------------|

| SDK-LH7A404-11-6416 <sup>1</sup> | CENGLH7A404-11-504HC <sup>1</sup> | \$399              |

| SDK-LH7A404-11-6416R             | CENGLH7A404-11-504HCR             | \$399              |

1. This is a non-RoHS configuration.

LOGIC

#### LOGIC WEBSITE :: DESIGN RESOURCES:

- +Logic Technical Support : http://www.logicpd.com/support/

- +Technical Discussion Group: http://www.logicpd.com/support/tdg/

- +Frequently Asked Questions (FAQ): http://www.logicpd.com/support/faq/

- +For more information contact Logic Sales : product.sales@logicpd.com

#### embedded product solutions

411 N. Washington Ave. Suite 400 Minneapolis, MN 55401 T: 612.672.9495 F: 612.672.9489 I: www.logicpd.com

#### **Product Features**

#### Processor

+Sharp ARM 922TDMI LH7A404 microprocessor running up to 200 MHz

#### **SDRAM Memory**

+64 MB SDRAM standard

#### Flash Memory

+16 or 32 MB NOR

#### Display

- +Programmable color LCD controller

- +Built-in driver supports up to 1024x768 with 8-bit LCD interface

#### Touch Screen

+Integrated 4-wire touch screen controller

#### **Network Support**

+10/100 Base-T Ethernet controller for application/debug (SMSC LAN 91C111)

#### Audio

+AC97audio codec

#### **PC Card Expansion**

- +CompactFlash Type I card (memory-mapped mode only)

- +Smart Card, MMC/SD, dual PCMCIA interfaces

#### USE

- +Two USB 2.0 full-speed host interfaces

- +One USB 2.0 full-speed device interface

#### Serial Ports

+Three 16C550 compatible UARTs

#### SSP

+Supports Motorola SPI, National Semiconductor MICROWIRE, TI SSI

#### **GPIO**

+Programmable I/O depending on peripheral requirements

#### Software

- +LogicLoader<sup>™</sup> (bootloader/monitor)

- +Windows CE 5.0 BSP

#### Mechanical

+60.2 mm wide x 67.8 mm long x 4.4 mm high

#### **RoHS Compliant**

PN: 1000571 Rev D

# 1.2 Acronyms

ACI Audio CODEC Interface

ADC Analog to Digital Converter

AFE Analog Front End Interface

AHB Advanced Hardware Bus

BSP Board Support Package

CPLD Complex Programmable Logic Device

DAC Digital to Analog Converter

DC Direct Current

DMA Direct Memory Access

DRAM Dynamic Random Access Memory

ENDEC Encoder Decoder

ESD Electro Static Dissipative

FET Field Effect Transistor

FIQ Fast Interrupt Request

FIFO First In First Out

GPIO General Purpose Input Output HAL Hardware Abstraction Laver

IC Integrated Circuit

I2S Inter-IC Sound

I/O Input/Output

IRQ Interrupt Request

LCD Liquid Crystal Display

LOLO LogicLoader™ MMC Multi Media Card NC No Connect PHY Physical Layer PLL Phase Lock Loop

PMOS P Metal Oxide Semiconductor

RTC Real Time Clock

SDK Starter Development Kit

SDRAM Synchronous Dynamic Random Access Memory

SIR Serial Infrared

SoC System on Chip

SOM System on Module

SSP Synchronous Serial Port

SPI Standard Programming Interface

TSC Touch Screen Controller

TTL Transistor-Transistor Logic

UART Universal Asynchronous Receive Transmit

UHCI Universal Host Controller Interface

VIC Vectored Interrupt Controller

## 1.3 Technical Specification

Please refer to the following component specifications and data sheets.

LH7A404-11 Card Engine IO Controller Interface Specification

LogicLoader<sup>TM</sup> User's Manual

LH7A404 Universal Microcontroller User's Guide

Xilinx Coolrunner™-II CPLD Product Specification (XC2C128-7VQG100C)

Xilinx Device Package User Guide

Wolfson WM9708 AC97 Audio CODEC data sheet

# 1.4 Card Engine Interface

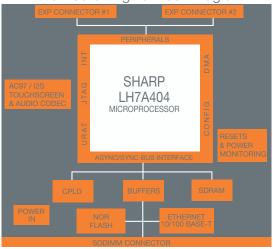

Logic's common Card Engine interface allows for easy migration to new processors and technology. Logic is constantly researching and developing new technologies to improve performance, lower cost, and increase feature capabilities. By using the common Card Engine footprint, it is possible to take advantage of Logic's work without having to re-spin the old design. Contact Logic sales for more information.

Figure 1.1: Card Engine Advantages

In fact, encapsulating a significant amount of your design onto the Card Engine reduces any long-term risk of obsolescence. If a component on the Card Engine design becomes obsolete, Logic will simply design for alternative part that is transparent to your product. Furthermore, Logic tests all Card Engines prior to delivery, decreasing time-to-market and ensuring a simpler and less costly manufacturing process.

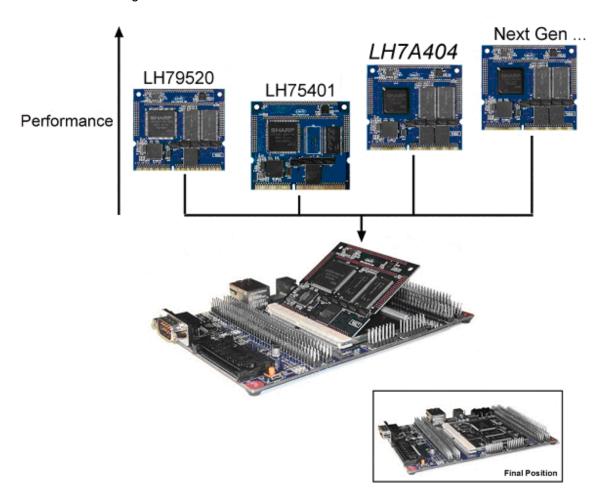

# 1.5 LH7A404-11 Card Engine Block Diagram

Figure 1.2: LH7A404-11 Card Engine Block Diagram

# 1.6 Electrical, Mechanical, and Environmental Specifications

## 1.6.1 Absolute Maximum Ratings

| Parameter                           | Symbol        | Rating      | Unit |

|-------------------------------------|---------------|-------------|------|

| DC IO and Peripheral Supply Voltage | 3.3V          | -0.3 to 4.6 | V    |

| DC uP and SDRAM Supply Voltage      | 3.3V_uP_SDRAM | -0.3 to 4.6 | V    |

| DC Core Supply Voltage              | VCORE         | -0.3 to 2.4 | V    |

**NOTE:** These stress ratings are only for transient conditions. Operation at or beyond absolute maximum rating conditions may affect reliability and cause permanent damage to the Card Engine and its components.

## 1.6.1.1 Recommended Operating Conditions

| Parameter                                  | Min        | Typical    | Max        | Unit   | Notes |

|--------------------------------------------|------------|------------|------------|--------|-------|

| DC IO & Peripheral Supply Voltage          | 3.0        | 3.3        | 3.6        | V      | 1     |

| DC IO Supply Active Current                | _          | 196        | 286        | mA     | 2     |

| DC uP IO and SDRAM Supply Voltage          | 3.0        | 3.3        | 3.6        | V      |       |

| DC uP IO and SDRAM Supply Current          | _          | 48         | 66         | mA     |       |

| DC Core Supply Voltage                     | 1.71       | 1.8        | 1.89       | V      | 1     |

| DC Core Supply Active Current              | _          | 126        | 222        | mA     | 2     |

| Commercial Operating Temperature           | 0          | 25         | 70         | °C     |       |

| Industrial Operating Temperature           | -40        | 25         | 85         | °C     | 3     |

| Storage Temperature                        | -40        | 25         | 85         | °C     |       |

| Dimensions                                 | _          | 2.35 x 2.6 | _          | Inches |       |

| Weight                                     | _          | 17         | _          | Grams  | 4     |

| Connector Insertion/Removal                | _          | 50         | _          | Cycles |       |

| Input Signal High Voltage                  | _          | 2.0        | _          | V      |       |

| Input Signal Low Voltage                   | _          | 0.8        | _          | V      |       |

| Output Signal High Voltage                 | 2.6        | _          | VIO        | V      |       |

| Output Signal Low Voltage                  | GND        | _          | 0.4        | V      |       |

| Processor Core Crystal Frequency Tolerance | 14744.8627 | 14745.6000 | 14746.3373 | kHz    | 5,6,7 |

| Processor RTC Crystal Frequency Tolerance  | 32.7670    | 32.7680    | 32.7690    | kHz    | 5,8   |

#### NOTES:

- 1. Core voltage must never exceed IO and peripheral supply voltage.

- 2. This test was performed with the 91C111 chip power disabled.

- 3. Contact Logic for more information on an industrial temperature LH7A404-11 Card Engine

- 4. May vary depending on Card Engine configuration.

- 5. Min and Max values are based on the Min and Max tolerance of the processor datasheet.

- 6. The Min and Max values shown include the variation in frequency including the tolerance at 25 °C and the stability variation over temperature.

- 7. Core crystal tolerance requirement of processor is ±50 ppm.

- 8. RTC crystal tolerance requirement of processor is ±30 ppm.

**NOTE:** Sharp recommends that the 1.8V power supply be energized before the 3.3V supply. If this is not possible, the 1.8V supply may not lag the 3.3V supply by more than 100 microseconds. If longer delay time is needed, it is recommended that the voltage difference between the two power supplies be within 1.5V during power supply ramp up.

# 2 Electrical Specification

#### 2.1 Microcontroller

#### 2.1.1 LH7A404 Microcontroller

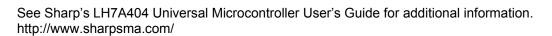

The LH7A404-11 Card Engine uses Sharp's highly integrated system on a chip LH7A404 microcontroller. This SoC possesses a 32-bit ARM922T RISC core and provides many integrated on-chip peripherals including:

## Integrated ARM922T™ Core

- □ 32-bit ARM922T<sup>TM</sup> RISC Core

- □ 16kB Cache: 8kB Instruction Cache and 8kB Data Cache

- □ MMU

- □ 4 GB logical address space

# 80 KB on-chip SRAM Integrated LCD Controller

- □ Up to 800 x 600 Resolution at 16-bit color

- o (1024 x 786 at 8 bits color)

- □ Supports STN, TFT, and HR-TFT

- □ Up to 65,536 Colors

Three UARTs

Classic IrDA (up to 115.2 Kbps)

SSP interface

AC97 CODEC Interface

1 USB Client and 1 USB host Interface (USB 1.1)

MultiMediaCard/Secure Digital interface

Smart Card interface (ISO7816)

Smart Battery Monitor Interface

Up to 64 General Purpose I/O Signals

Two 16-bit Pulse Width Modulators

□ Ten fully independent DMA Channels

Three Programmable Timers RTC Boot ROM Low Power Modes 5-Volt Tolerant Inputs

**IMPORTANT NOTE:** Please see http://www.sharpsma.com/ for errata on the LH7A404.

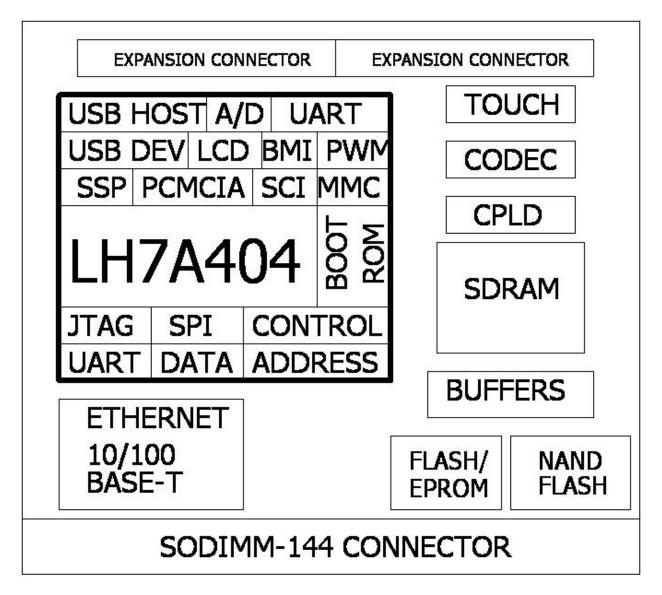

## 2.1.2 LH7A404 Microcontroller Block Diagram

Figure 2.1: LH7A404 Microcontroller Block Diagram

## 2.2 Clocks

The LH7A404 requires 2 crystals in order to enable proper internal timing. The first, a 14.7456 MHz crystal, is used to generate many of the processor's internal clocks via a series of signal dividers. To generate the FCLK signal, for example, the 14.7456 MHz signal is run through a PLL in which the divisor is set in the Clock Set register. FCLK is then used internally as the Synchronous Bus Mode core clocking for the ARM922T core and cache. The 14.7456 MHz signal is also used to create the HCLK, HCLK\_CPU, PCLK, and peripheral clock signals. One such peripheral clock is set up through a separate PLL to produce a 48.0 MHz clock for USB operations. An additional signal that stems from the crystal input is the uP\_AUX\_CLK signal; it is produced through a programmable divider on the Card Engine. The uP\_AUX\_CLK is provided on the 144-pin SODIMM expansion connector as the LH7A404 CLKOUT, and is set to a default of 14.7456MHz.

**IMPORTANT NOTE:** Please see Sharp's LH7A404 Universal Microcontroller User's Guide for additional information about the relationship between FCLK and HCLK.

The second required crystal runs at 32.768 kHz and is the only permanently running clock in the LH7A404. Because this clock runs regardless of the processor's state, a ripple divider is used in order to reduce power consumption during the halt and standby states. This divider produces the 1 Hz signal for the RTC interface as well as intermediate frequencies of 16 kHz and 8 kHz for the state controller and PLL interlocks.

The LH7A404 is able to operate in three different clocking modes: asynchronous, synchronous, or FastBus extension. Each of the three has certain advantages or disadvantages in system throughput and power consumption, depending on the whether the end application is CPU-, memory-, or peripheral-intensive. Refer to the LH7A400 Universal Microcontroller User's Guide for information on the specific advantages/disadvantages of each bus-clocking mode

The LH7A404's microcontroller core clock speed is initialized to 200 MHz on the Card Engine and the Bus speed is set at 100 MHz in the LogicLoader<sup>™</sup>. Other clock speeds can be supported and modified in software for specific user applications, such as a specific serial baud rate.

The LH7A404-11 Card Engine provides an external Bus clock, uP\_BUS\_CLK, on the 144-pin SODIMM connector. The uP\_BUS\_CLK, which is connected to the processor's SCLK, is set to a default of 100 MHz. SCLK also serves as the SDRAM and CPLD clock on the LH7A404-11 Card Engine.

| LH7A404 Microcontroller Signal Name | LH7A404-11 Card Engine<br>Net Name | Default Software Value in<br>LogicLoader™ |

|-------------------------------------|------------------------------------|-------------------------------------------|

| FCLK                                | N/A                                | 200 MHz                                   |

| HCLK                                | N/A                                | 100 MHz                                   |

| SCLK                                | uP_BUS_CLK                         | 100 MHz                                   |

| PGMCLK                              | uP_AUX_CLK                         | 14.7456 MHz                               |

## 2.3 Memory

#### 2.3.1 Synchronous DRAM

The LH7A404-11 Card Engine uses a 32-bit memory bus to interface to SDRAM. The memory can be configured as 16, 32, or 64 MB in order to meet the user's memory requirements and cost constraints. Logic's default memory configuration on SDK boards is specified as 32 MB.

## 2.3.2 Direct Memory Access (DMA)

The Sharp LH7A404 microcontroller has an internal DMA controller that offers 10 fully independent channels. These channels can be used to interface streams from 20 internal peripherals to the system memory (including USB, SD/MMC, AAC, and all three UARTs). The DMA controller can also be used to interface streams from Memory to Memory or Memory to External Peripheral using 2 dedicated M2M channels. External handshake signals are available to support transfers to/from external peripherals. For more information on using the DMA refer to the LH7A404 Universal Microcontroller User's Guide.

#### 2.3.3 NOR Flash

The LH7A404-11 Card Engine uses a 32-bit memory bus (split into 2, 16-bit channels, one to each flash memory) to interface to Intel StrataFlash memory chips. The onboard Card Engine memory can be configured as 8, 16, or 32 MB to meet the user's flash requirements and cost constraints. Logic's default flash configuration is 16 MB on the SDK. Because flash is one of the most expensive components on the LH7A404-11 Card Engine, it is important to contact Logic when determining the necessary flash size.

It is possible to expand the system's non-volatile storage capability by adding external flash IC's, CompactFlash, or NAND flash. See the LH7A404-11 Application Kit for reference designs or contact Logic for other possible peripheral designs.

#### 2.3.4 NAND Flash

The LH7A404-11 Card Engine can be configured to boot from and use NAND flash. This functionality is currently under development, please contact Logic for more information.

#### 2.3.5 EPROM

The LH7A404-11 Card Engine can be configured to boot from on board EPROM. This functionality is currently under development, please contact Logic for more information.

#### 2.3.6 CompactFlash (memory-mapped mode only)

The LH7A404-11 Card Engine supports a CompactFlash memory-mapped mode only slot that compliments the processor's standard dual PC card support. The LH7A404-11 Card Engine uses the CPLD to provide the necessary signals for a CompactFlash card interface in memory-mapped mode only. The Zoom SDK reference design includes a CompactFlash connector for memory-mapped mode, but does not support hot-swappable capability. If hot-swappable capability is desired, it can be achieved by adding further hardware on the user's base-board. See the LH7A404-11 CPLD IO controller specification for further details on the use of CompactFlash.

**IMPORTANT NOTE:** The CPLD CompactFlash interface supports memory-mapped mode only. Use the LH7A404 processor's PC card slots for more PC card mode options.

## 2.4 Secure Digital (SD) and MultiMediaCard (MMC)

The LH7A404-11 Card Engine provides one SD/MMC adapter that can be used as an MMC card or SD card. This controller supports the full MMC/SD bus protocol identified in the MMC System Specification 2.11 and SD Memory Card Specification Version 1.0. The controller can also implement a SPI interface to either card. For more detailed operation and programming operations see the MultiMediaCard Association and SD Card System Specifications, available at www.mmca.org and www.sdcard.org. respectively.

# 2.5 PCMCIA/CompactFlash (external)

Both PCMCIA and CompactFlash devices are externally supported on the LH7A404 Card Engine. To handle these devices, the static memory controller has allocated two of the eight configurable memory banks for PCMCIA and CompactFlash interfaces. The Card Engine can directly support one PCMCIA/CompactFlash card and has the capability to interface to two cards with minimal external circuitry through the CPLD. In order to properly take advantage of these features software parameters need to be set; see Chapter 5: "Static Memory Controller" in the LH7A404 Universal Microcontroller User's Guide for more information.

## 2.6 10/100 Ethernet Controller

The LH7A404-11 Card Engine uses the SMSC 91C111 10/100 single chip Ethernet Controller to provide an easy-to-use networking interface. To facilitate use, six signals from the 91C111 are mapped to external connectors: transmit plus/minus, receive plus/minus, and two status LED's. The four analog PHY interface signals (transmit/receive) each require an external impedance matching circuit to operate properly. Logic provides an example circuit schematic in the LH7A404-11 Application Kit for reference.

**IMPORTANT NOTE:** The ENEEP signal on the SMSC 91C111 is connected to a zero ohm resistor that is not populated. This is because the ENEEP signal has a weak internal pull-up in the SMSC 91C111and if the signal is tied low it low will disable the serial EEPROM interface.

## 2.7 Audio CODEC

The LH7A404 processor has an internal AC97 controller that is compliant with the Audio CODEC '97 Component Specification, v2.2. This AC97 Controller implements a 5-pin serial interface to the AC97 Audio CODEC, in this case the Wolfson WM9708. From the Wolfson CODEC on the LH7A404-11 Card Engine there are 3 outputs, CODEC\_OUTL, CODEC\_OUTR, and MFP34 – MONO\_OUT. All of these signals are available from the 80-pin expansion connectors.

**NOTE:** More information about the Intel AC97 standard is available on Intel's website at http://www.intel.com/design/chipsets/hdaudio.htm.

The Wolfson CODEC on the LH7A404 Card Engine performs full duplex 18-bit CODEC functions and supports variable sample rates from 8-48k samples/second. The Wolfson chip also has an onboard 24.576 MHz crystal which is used for the AC97 master clock frequency.

**NOTE:** The Sharp LH7A404 also offers an ACI interface for non-AC97 CODEC devices. This interface provides a digital 8-bit interface that is multiplexed with the signals from the AC97 controller. If you are looking for a different CODEC option, Logic has previously interfaced different high performance audio CODECs into other Card Engines. Contact Logic for assistance in selecting an appropriate audio CODEC for your application.

#### 2.8 Video Interface

Sharp's LH7A404 microcontroller has a built in LCD controller supporting STN, Color STN, HR-TFT, AD-TFT, TFT panels at up to 800 x 600 x 16-bit or 1024 x 768 x 8-bit color resolution. See the LH7A404 Universal Microcontroller User's Guide for further information on the integrated LCD controller. The signals from the LH7A404's LCD controller are organized by bit and color and can be interfaced through the J1A expansion connectors. Logic has written drivers for numerous panels of different types and sizes. Please contact Logic before selecting a panel for your application.

**IMPORTANT NOTE:** Using the internal graphics controller will affect processor performance. Selecting display resolutions and color bits per pixel will vary processor busload.

## 2.9 Serial Interface

The LH7A404-11 Card Engine comes with the following serial channels: UARTA, UARTB, UARTC, and SSP. If additional serial channels are required, please contact Logic for reference designs. UARTC supports both wired serial and infrared communications, supporting a digital encoded output and decoded input without analog processing. Please see the LH7A404 Universal Microcontroller User's Guide for further information regarding serial communications.

## 2.9.1 UARTA

UARTA has been configured to be the LH7A404-11 development kit's main serial port. It is an asynchronous 16C550-compatible UART. This UART provides a high-speed serial interface that uses FIFO and is capable of sending and receiving serial data simultaneously. The signals from the Card Engine are TTL level signals not RS232 level. The user must provide an external RS232 transceiver for RS232 applications. Logic has provided an example reference design with the SDK kit. When choosing an RS232 transceiver, the user should keep in mind cost, availability, ESD protection, and data rates.

UARTA's baud rate is set by default to 115.2K bits/sec, though it supports all common serial baud rates from 2.4kbps to 460.8kbps. UARTA is available off the J1C 144-pin SODIMM connector.

#### 2.9.2 UARTB

Serial Port UARTB is an asynchronous 16C550 compatible UART. This UART is a high-speed serial interface that uses FIFO, and it is capable of sending and receiving serial data simultaneously. The signals from the Card Engine are TTL level signals, not RS232 level. The user is responsible for providing an external RS232 transceiver for RS232 applications. UARTB's baud rate can be set to all common serial baud rates from 2.4kbps to 460.8kbps.

The UARTB pins are multiplexed with GPIO Ports B1-B5; when UARTB is not in use, the GPIO pins can be used instead. UARTB is available off the J1B 80-pin expansion connector.

#### 2.9.3 **UARTC**

Serial Port UARTC has dual functionality; UARTC supports both serial communications (similar to UARTA/B) and infrared communications. When functioning as a serial port, UARTC will perform many of the characteristics as discussed for UARTA/B, except that UARTC does not have any status signals. If status signals are desired, it is necessary to map these control signals to GPIO ports.

In order to define UARTC's functionality, a programmable register is available to specify infrared or serial operation. Once one communication is chosen, the pins for the other connection are ignored, and vice-versa. The pins used for UARTC's functions are uP\_IRTX and uP\_IRRX (infrared) and uP\_UARTC\_RX and uP\_UARTC\_TX (serial), available off the J1B 80-pin expansion connector. Because there are two sets of transmission signals, UARTC's serial transmit and receive pins are multiplexed with GPIO Ports B0 and C0, becoming available GPIO pins when Infrared communications are not being used (the two sets of signals would otherwise be redundant). Refer to Sharp's LH7A404 Universal Microcontroller User's Guide for more information on using infrared communications.

#### 2.9.4 SSP/SPI

The SSP interface on the LH7A404 Card Engine supports three data frame formats:

- □ Texas Instruments' SSI

- Motorola SPI

- National Semiconductor Microwire

Logic has chosen to implement Motorola's SPI interface as the default setting. If another interface is desired, programming the Control Register 0's 2-bit Frame Format field allows the default settings to be adjusted. The SPI format is used to interface between the parallel data inside the SoC and synchronous serial communications on slave peripheral devices. The SPI interface is master-only, with programmable clock rate and pre-scale options that are used to generate the appropriate bit-rate and Serial Clock output. The Data Size Specification is also configurable, and as such the SPI port can receive or transport anywhere from 4 to 16 bits. The SPI signals are available off the 144-pin SODIMM connector. Please see the LH7A404 Universal Microcontroller User's Guide for further information.

## 2.10 Keyboard and Mouse Interface (KMI)

The LH7A404 KMI implements a standard IBM PS2 or AT-compatible keyboard and mouse interface and complies with the AMBA specification rev 2.0. Communications with the KMI can be initiated through polling or interrupts. Furthermore, the interface offers a programmable clock divider, odd-bit parity generation/checking, and open drain outputs. Refer to Sharp's LH7A404 Universal Microcontroller User's Guide for more information about using a keyboard or mouse with the LH7A404-11 Card Engine.

#### 2.11 USB Interface

The LH7A404 Card Engine is configured with both USB Host and Device functionality. The USB device interface is compliant to the USB 1.1 specification and both the OpenHCI and Intel UHCI specifications. This USB client supports full-speed (12 Mbits/sec) operation and both suspend and resume signaling. The USB device interface on the LH7A404 is able to transmit, receive data, or control information over the bus, and is available for external use off the J1A 80-pin connector.

The USB Host interface is compatible with both the USB 1.1 and OpenHCI 1.0 specifications. This controller also supports both low speed and high-speed USB devices and features a root hub with two downstream ports. The four signal USB connector signals are available off the J1A 80-pin connector while the host interface control functions are available can be accessed through jumper signals off the J1B 80-pin connector (see Section 5.4). For more information on using both the USB device and host interfaces, please see the LH7A404 Universal Microcontroller User's Guide for more information on using both the USB device and host interfaces.

**IMPORTANT NOTE:** In order for USB to be correctly implemented on the LH7A404 Card Engine, additional impedance matching circuitry is required on the USBP and USBM signals before they can be used. USB 1.1 requirements specify that the impedance on each driver must be between  $28\Omega$  and  $44\Omega$ . For reference, see the impedance matching circuit on the Logic SDK board.

#### 2.12 ADC/Touch Interface

The LH7A404-11 Card Engine offers a 10-bit analog-to-digital converter (ADC). This ADC also can be used to implement a touch screen controller (TSC), supporting standard 4-wire resistive touch panels. This TSC supports up to 8-wire touch screens—if more than 4-wire operation is desired, please see the application note *Using the SHARP ADC with Resistive Touch Screens*, available at http://www.sharpsma.com/. The other six A/D signals are available externally off the J1A and J1B 80-pin connectors. Please see the LH7A404 Universal Microcontroller User's Guide for more information.

## 2.13 General Purpose I/O

Logic designed the LH7A404-11 Card Engine to be flexible and provided multiple options for analog and digital GPIO. There are numerous digital GPIO pins on the Card Engine that interface to the LH7A404 and the Xilinx CPLD. Some of these GPIO pins are interrupt capable while other signals are input or output only—see the Pin Descriptions section of this data sheet for more information on these options. If certain peripherals are not desired, such as the LCD Controller, Chip Selects, IRQs, UARTS, AC97, PCMCIA and CompactFlash, Smart Card Interface, or BMI interface, then multiple GPIO pins become available. Please see the table in Section 5.5 for a list of the available GPIO trade-offs.

#### 2.14 CPLD

Please see the LH7A404-11 Card Engine IO Controller Specification for CPLD information.

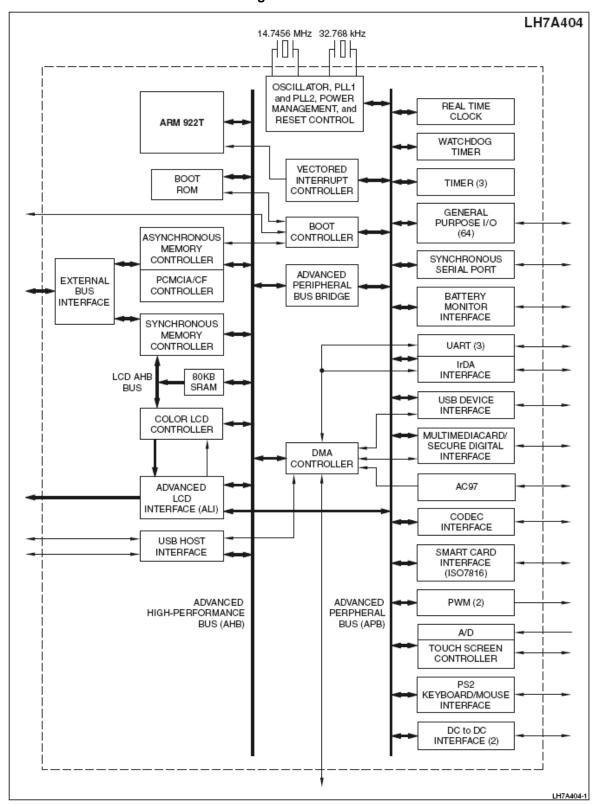

#### 2.15 Serial EEPROM Interface

Logic designed the LH7A404-11 Card Engine to have a low-cost 1 kbit serial EEPROM for non-volatile data storage. The serial EEPROM is connected to the LH7A404 microcontroller via the CPLD through an SPI interface – discussed in the touch screen controller section above. See Figure 2.2 below. For more information please view the LH7A404-11 Card Engine CPLD Interface Specification.

Figure 2.2: Serial EEPROM Block Diagram

## 2.16 Expansion/Feature Options

The LH7A404-11 Card Engine was designed for expansion and a variable feature set, providing all the necessary control signals and bus signals to expand the user's design. Some of these signals are buffered and brought out to the 144-pin SODIMM connector and two 80-pin expansion connectors. It is possible for a user to expand the Card Engine's functionality even further by adding PCI or ISA devices. Some features that are implemented on the LH7A404, but are not discussed herein, include: PWM, DC-DC, BMI, and ACI setup. See the LH7A404 Universal Microcontroller User's Guide and the LH7A404-11 Card Engine schematics for more detail. Logic has experience implementing additional options, including other audio codecs, Ethernet IC's, co-processors, and components on the Card Engine boards. Please contact Logic for potential reference designs before selecting your peripherals.

# 3 System Integration

## 3.1 Configuration

The LH7A404-11 Card Engine was designed to meet multiple applications for specific users and budget requirements. As a result, this Card Engine supports a variety of embedded operating systems and comes with the following hardware configurations:

- ☐ Flexible memory footprint: 16, 32, or 64 MB SDRAM

- ☐ Flexible flash footprint: 8, 16, or 32 MB StrataFlash

- Optional SMSC 91C111 10/100 Ethernet Controller

- □ Optional Wolfson WM9708 Audio CODEC

Please contact Logic for additional hardware configurations to meet your application needs.

#### 3.2 Resets

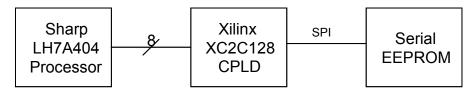

#### 3.2.1 Master Reset (Hard Reset)

All hardware peripherals should connect their hardware-reset pin to the MSTR\_nRST signal on the SODIMM connector. Internally all Card Engine peripheral hardware reset pins are connected to either the MSTR\_nRST net or to the RESET\_HIGH net as shown in the figure below. The MSTR\_nRST signal is an open-drain output, enabling the user to assert the MSTR\_nRST signal externally. Logic suggests that custom designs implemented with the LH7A404-11 Card Engine use the MSTR\_nRST signal as the "pin hole" reset used in commercial embedded systems.

Figure 3.1: Reset Circuit

If the output of the reset chip, MSTR\_nRST, is asserted (active low), the user can expect to lose information stored in SDRAM. The data loss occurs because the external signals uP\_BUS\_CLK and uP\_AUX\_CLK are interrupted during the assertion of the MSTR\_nRST signal. The RESET\_HIGH signal, on the other hand, is the active high output of the reset circuit and is not provided as part of the Card Engine connector interface.

**IMPORTANT NOTE:** Any custom reset circuit design should guard the assertion of the reset lines during a low power state so as to prevent power-up in a low or bad power condition (which will cause data corruption and possible temporary system lockup). See Section 3.5.2 for further details.

There following three conditions will cause a system-wide reset: power-on, a low pulse on the MSTR\_nRST signal, and the power fail comparator input (PFI pin) falling below the internal comparator threshold.

#### Power On:

At power on, the MSTR\_nRST signal is asserted low when the supply voltage (VDD) of the reset chip is between 0.4V and 2.941V. Once the 3.3V\_uP\_SDRAM supply surpasses 2.941V the reset chip will trigger a rising edge of MSTR\_nRST after a 65 to 195ms delay (130 ms typical).

## Low Pulse on MSTR\_nRST Signal:

A low pulse on the MSTR\_nRST signal of the reset chip, asserted by an external source (for example, the reset button on the custom design application) will bring MSTR\_nRST low until the assertion source is de-asserted. There is no delay beyond the de-assertion of the external MSTR\_nRST signal source, so the custom design must ensure that the assertion time is sufficient for all related peripherals.

Logic suggests that any external assertion source that triggers the MSTR\_nRST signal, analog, or digital de-bouncing be used to generate a clean one shot reset signal.

#### Power Fail:

If the power fail comparator input pin (PFI pin) falls below the internal comparator threshold of 0.551V, it will create a low pulse on the MR input pin of the reset chip. The low assertion of the MR pin will assert the MSTR\_nRST signal and will hold it low after the MR pin is de-asserted (PFI is above the comparator level and power is restored) for 65 to 195 ms (130 ms typical). Please see the TI TPS3103 data sheet at http://www.ti.com for additional details on reset timing and thresholds.

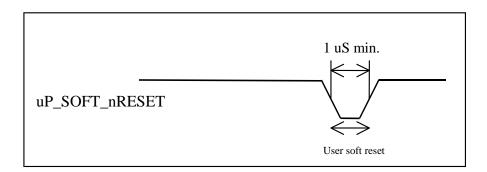

#### 3.2.2 Soft Reset

Logic has created a soft reset signal, SW\_nRESET, designated as a reset for the LH7A404's internal registers without affecting the peripherals on the rest of the board or the data stored in SDRAM. The data is saved because the SDRAM controller automatically places the SDRAM in self-refresh before the uP\_SD\_CLK clock is disabled. As in the Standby state described in Section 3.5.4.2, the 32.768 kHz clock continues running, allowing the system to properly wake up. The SW\_nRESET signal is an input to the LH7A404 processor's user reset input pin.

Figure 3.2: Soft Reset

See Sharp's LH7A404 Universal Microcontroller User's Guide for additional information on register conditions after a soft (manual) reset.

## 3.3 Interrupts

The LH7A404 incorporates two Vectored Interrupt Controllers (VIC1 and VIC2): the advantage being that a vectored interrupt has improved latency as it provides direct information where service routines are located, eliminating the need for levels of software arbitration. Through these two interrupt controllers the LH7A404 can prioritize and process up to 64 interrupts (40 internal). Figure 3.3 shows a list of the interrupt hierarchy, ordered by priority. All VIC1 interrupts have a higher priority than any VIC2 interrupts. In both VICs, FIQ interrupts have the highest priority, followed by interrupt vector 0 through interrupt vector 15; non-vectored IRQ interrupts have the lowest priority. Refer to Sharp's LH7A404 Universal Microcontroller User's Guide for further information on using IRQ and FIQ interrupts.

| VIC  | INTERRUPT TYPE                           |

|------|------------------------------------------|

| VIC1 | FIQ Interrupt(s)                         |

| VIC1 | Vectored Interrupts 0-15 (in that order) |

| VIC1 | Non-vectored Interrupts                  |

| VIC2 | FIQ Interrupt(s)                         |

| VIC2 | Vectored Interrupts 0-15 (in that order) |

| VIC2 | Non-vectored Interrupts                  |

Figure 3.3: Interrupt Priorities (high to low)

**NOTE:** The CPLD interrupts the processor via the uP\_nIRQE signal. This signal is a FIQ interrupt (PF4) in VIC2.

## 3.4 JTAG Debugger Interface

The JTAG connection on the LH7A404 allows recovery of corrupted flash memory and real time applications debug. When choosing a debugger board, remember that many different third-parties' JTAG debuggers are available for Sharp ARM microcontrollers. The following signals make up the JTAG interface to the LH7A404: uP\_TDI, uP\_TMS, uP\_TCK, and uP\_TDO. These signals should interface directly to a 20-pin 0.1" through-hole connector as demonstrated in the Sharp LH7A404 Universal Microcontroller User's Guide, or as shown on reference schematics.

**IMPORTANT NOTE:** When laying the 20-pin connector out, realize it may not be numbered as a standard 20-pin 0.1" IDC through-hole connector. See LH7A404-11 SDK reference design for further details. Different IC manufacturers define the 20-pin IDC connector pin-out differently.

**IMPORTANT NOTE ON USING JTAG:** The Sharp LH7A404 processor requires a rising edge on the processor wake-up signal to bring the processor from Cold Boot state to run state. Therefore, in order to use JTAG operation on the LH7A404-11 Card Engine, one must consult their JTAG manufacturer to find when the JTAG device requires the processor to be in the Run state. If the JTAG device issues a reset to the processor, then the wake-up signal must transition from low to high to return to the Run state before the JTAG debugger may connect. The JTAG device may be able to connect to the processor while it is in Standby state, but will not be able to do anything that requires processor functioning until woken.

## 3.5 Power Management

## 3.5.1 System Power Supplies

In order to ensure a flexible design, the LH7A404-11 Card Engine was designed to have the following five power areas, 3.3V\_uP\_SDRAM, 3.3V, 3.3VA, 3.3V\_WRLAN, and VCORE. All power areas are inputs to the Card Engine with the exception of 3.3V\_WRLAN, which is an output from the Card Engine.

## 3.5.1.1 3.3V\_uP\_SDRAM

The 3.3V\_uP\_SDRAM input pins are connected to a 3.3V power supply with an optional backup battery. If the design is required to maintain SDRAM contents in a critical power situation (low battery, loss of power), the 3.3V\_uP\_SDRAM supply should be maintained above the minimum level at all costs (see Section 2 "Electrical Specification"). Logic suggests using Standby mode to prepare the system for a critical power condition. In this way, the SDRAM is placed into self-refresh and processor is placed into the Standby state. Please note the description of Standby mode in this section below.

#### 3.5.1.2 3.3V

The power nets connected to the 3.3V power plane handle the majority of the peripheral supply pins (digital) on the LH7A404-11 Card Engine. This supply must stay within the acceptable levels specified in the "Electrical Specification" section of this manual, unless experiencing power down or critical power conditions.

Under critical power conditions, Logic suggests notifying the system through the assertion of a Standby sequence first, and then powering this supply off.

#### 3.5.1.3 3.3VA

The power nets connected to the 3.3VA power plane handles all peripheral supply pins (analog), but not the LH7A404 processor on the LH7A404-11 Card Engine. The 3.3VA supply must stay within the acceptable levels specified in the "Electrical Specification" section of this manual, unless powering down the board or under critical power conditions. Under critical power conditions, Logic suggests first notifying the system through the assertion of a Standby sequence and then powering this supply off.

## 3.5.1.4 3.3V\_WRLAN

This "power" supply net is an output from the Card Engine and is controlled through a registered bit in the on-board CPLD. For more details on this specific control bit, see the *LH7A404 Card Engine IO Controller Specification* manual. Logic's software BSP asserts this signal in order to properly manage power in the LAN91C111 Ethernet chip. However, this management does not put the part in a low enough power state for many applications.

The custom application board should use the 3.3V\_WRLAN output pin to supply the Ethernet impedance matching resistors with power. These resistors should not be connected to 3.3V directly or the entire Ethernet controller circuit on the Card Engine will try to power itself through the impedance matching resistors. Please see Logic's schematics for the SDK reference designs for details.

**IMPORTANT NOTE:** The purpose of the 3.3V\_WRLAN power plane on the Card Engine is to power the 91C111 chip separately and allow for a complete, but independent, shut down. Furthermore, the 3.3V\_WRLAN output from the Card Engine is required to completely isolate the LAN circuit so that it is not back powered through the impedance matching resistors.

#### 3.5.1.5 VCORE

The analog power pins on the LH7A404 are connected to the VCORE voltage with low-pass filtering. The VCORE input pins are connected to a 1.8V power supply with an optional backup battery. If the design is required to maintain SDRAM contents in a critical power situation (low battery, loss of power), the VCORE supply should be maintained above the minimum level at all costs (see "Electrical Specification" section). Logic suggests using Standby mode to prepare the system for a critical power condition. In this way, the SDRAM is placed into self-refresh and the processor is placed into the Standby state. Please see the description of Standby mode later in this section.

#### 3.5.2 System Power Management

Good power management design is important in any system development and embedded system design is no exception. In embedded system design, power management is typically one of the most complicated areas due to the dramatic effect it has on the product cost, performance, usability, and overall customer satisfaction. Many factors affect a power-efficient hardware design: power supply selection (efficiency), clocking design, IC and component selection, etc. The LH7A404-11 Card Engine was designed to keep these aspects in mind and provide maximum flexibility in software and system integration.

On the LH7A404 there are many different software configurations that drastically effect power consumption: microcontroller core clock frequency, microcontroller bus clock frequency, microcontroller peripheral clocks, microcontroller bus modes (asynchronous, synchronous, FastBus), microcontroller power management states (run, halt, standby), peripheral power states and modes, product user scenarios, interrupt handling, and display settings (resolution, backlight, refresh, bits per pixel, etc). These settings are typically initialized in the startup software routines and may be later modified in the operating system and application software. Information for these items can be found in the appropriate documents such as the *LogicLoader Muser's Manual* or appropriate BSP manual.

**IMPORTANT NOTE**: Most of the LH7A404-11 Card Engine hardware architecture was designed for low power battery operated applications. The Xilinx CPLD, on the LH7A404-11 Card Engine design, was chosen to optimize cost over power savings. If power-optimization is the primary goal of the design; please contact Logic for other design configurations in this area.

## 3.5.3 Peripherals

Most peripherals provide software programmable power states. Sometimes, however, these programmable power states may not be the best solution. The SMSC 91C111 controller, for example, has software programmable power states which may not be sufficient for some applications. In order to solve this problem, Logic has provided hardware to cut power to the 91C111 chip. Please see the appropriate data sheets and the *LH7A404-11 Card Engine IO Controller Specification* for more information.

The LH7A404-11 Card Engine was designed to have the following five power areas, 3.3V\_uP\_SDRAM, 3.3V, 3.3V\_WRLAN, 3.3VA, and VCORE for a flexible hardware design. See Figure 3.3 below.

| Logic Net Name | Required<br>Input VDC                                         | Notes                                                                                                                                                                                                                     |

|----------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3V_uP_SDRAM  | 3.3VDC                                                        | Connects to the Processor's 3.3-volt pins and the SDRAM. This net can be used for battery powered or bridge battery applications that require the processor and the SDRAM to refresh.                                     |

| 3.3V           | 3.3VDC                                                        | Connects to the digital peripherals on the Card Engine.                                                                                                                                                                   |

| 3.3VA          | 3.3VDC                                                        | Connects to the Audio Codec on the Card Engine to provide a clean analog plane. The user may choose not to provide a clean analog plane depending on their performance requirements.                                      |

| VCORE          | 1.8V                                                          | Connects to the processor core voltage. See information on each specific processor for the VCORE voltage. Many processors require different VCORE voltages for different operating frequencies, temperatures, etc.        |

| 3.3V_WRLAN     | 3.3V<br>(This Pin is<br>an output,<br>see section<br>3.5.1.4) | Provides power to the SMSC 91C111 processor from the 3.3V area. The power to the 3.3V_WRLAN area is controlled by the signal WRLAN_ENABLE from the CPLD. See the IO Controller Specification for controlling this signal. |

**IMPORTANT NOTE:** Because the power management on the SMSC 91C111 is not suitable for many applications, the PMOS FET was added to control power input into the wired LAN.

Figure 3.4: Power Plane Diagram

#### 3.5.4 Microcontroller

The LH7A404 processor power management's scheme was designed to be easy to use. There are three power management states provided in the LH7A404 microcontroller: RUN, STANDBY, and HALT. Please see below for descriptions from all three states and the LH7A404 Universal Microcontroller User's Guide for more details

#### 3.5.4.1 Run Mode

Run is the LH7A404-11 Card Engine's normal operating stat in which both oscillator inputs and all clocks are hardware enabled. The LH7A404 can enter Run mode from either the Standby or Halt states. From the Standby state, Run can be accessed on three conditions: a rising-edge on the wakeup pin (the uP\_WAKEUP signal), an exit from the Clock Set register (after the clock divisor has been adjusted and the new clock output has stabilized), or the falling-edge of an interrupt (interrupts are active low). A Halt to Run transition occurs on the falling-edge of an interrupt (interrupts are active low). Power Fail, or on a user reset (see Figure 3.2: Soft Reset above).

**IMPORTANT NOTE**: Two seconds after a power on reset, a rising edge transition on the uP\_WAKEUP signal is required to transition from Standby to Run mode. The uP\_WAKEUP signal is pulled to 3.3V\_uP\_SDRAM on the Card Engine so a pushbutton tied to ground implementation can easily be used to provide the required low to high transition on the uP\_WAKEUP signal. The SDK kit has example circuitry for the required uP\_WAKEUP signal transition.

#### 3.5.4.2 Standby Mode

Standby is the LH7A404 Card Engine's hardware power down mode, allowing for minimal power consumption. In this mode, only the 32.768 kHz clock input is enabled and the Real Time Clock and state controller are the only active functional blocks. Before all the clocks are turned off, however, the SDRAM is put into self-refresh mode, and maintains the contents of memory while in the low power state. Standby mode can only be entered after a system power-on or on a progression from the Run state. A Run to Standby transition occurs on a Power Fail, User Reset (Soft Reset), Write Clock Set (new clock divisors specified), or read of the STBY register.

#### 3.5.4.3 Halt Mode

The Halt state is designed to reduce power consumption while the LH7A404 is waiting for an event such as a keyboard input. In this mode, although the processor clock is halted, the 14.7456 MHz oscillator input is enabled, thereby allowing software to specify the other active and inactive clocks. In this way, it is possible to maintain the LCD image yet reduce system-wide power usage at the same time. The only way to transition to the Halt state is on a read from the HALT register while in the Run state.

**IMPORTANT NOTE:** Although Halt consumes less power than Run mode, it consumes more power than the Standby Mode. Thus, on a power failure, the LH7A404 system will actually leave the Halt state and transition to the Standby state (the same thing occurs on an SW\_nRESET.

## 3.6 ESD Considerations

The LH7A404-11 Card Engine was designed to interface to a customer's peripheral board. The Card Engine was designed to be low cost and adaptable to many different applications. The LH7A404-11 Card Engine does not provide any on-board ESD protection circuitry—this must be provided by the product it is used in. Logic has extensive experience in designing products with ESD requirements. Please contact Logic if you need any assistance in ESD design considerations.

# 4 Memory & I/O Mapping

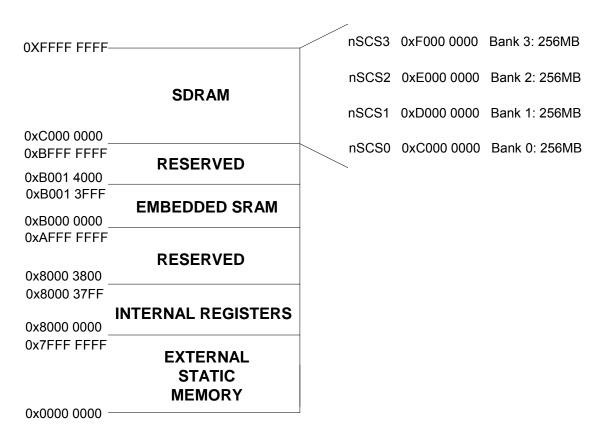

## 4.1 SDRAM Memory Map

Figure 4.1: LH7A404 SDRAM Memory Map

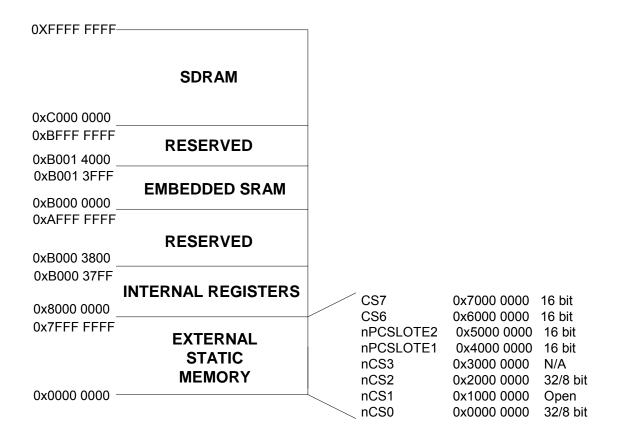

## 4.2 External Static Memory Map

Figure 4.2: LH7A404 Static Memory Map

**NOTE:** The bit numbers refer to the bank width at reset. Banks 0 and 2 (nCS0 and nCS2) are 32-bits wide if flash is used as the boot device and 8-bits wide if an EEPROM is used as the boot device.

## 4.2.1 Card Engine Static Memory Map Description

The table below describes how each bank of external static memory is used on the Card Engine.

| Bank | Chip Select | Start Address | Memory Description                |

|------|-------------|---------------|-----------------------------------|

| 7    | CS7         | 0x7000 0000   | IO Controller Peripherals (Fast¹) |

| 6    | CS6         | 0x6000 0000   | IO Controller Peripherals (Slow¹) |

| 5    | nPCSLOTE2   | 0x5000 0000   | Used for PC Card Interface        |

| 4    | nPCSLOTE1   | 0x4000 0000   | Used for PC Card Interface        |

| 3    | nCS3        | 0x3000 0000   | Open²                             |

| 2    | nCS2        | 0x2000 0000   | Boot Device (Flash or Off-Board)  |

| 1    | nCS1        | 0x1000 0000   | Video                             |

| 0    | nCS0        | 0x0000 0000   | Boot Device (Flash or Off-Board)  |

#### Notes:

- CPLD peripherals are components that get a decoded chip select from the CPLD. (i.e., CPLD memory mapped registers, onboard SMSC 91C111 Ethernet controller, etc. Please see the LH7A404-11 IO Controller Specification document for details.) These peripherals are separated into two different chip select banks, due to the difference in timing: slow and fast.

- 2. Chip Select 3 is multiplexed with the MultiMediaCard select signal.

## 4.2.2 Chip Select 6 (CS6)—CPLD Peripherals (slow timing)

The table below indicates how the CPLD decodes chip select 6. For more detailed information see the *LH7A404-11 IO Controller Specification*.

| Address Range             | Size      | Memory Description             |

|---------------------------|-----------|--------------------------------|

| 0x6000 0000 – 0x601F FFFF | 2MB       | Reserved                       |

| 0x6020 0000 – 0x603F FFFF | 2MB       | CF Chip Select                 |

| 0x6040 0000 – 0x605F FFFF | 2MB       | ISA-like Bus Chip Select       |

| 0x6060 0000 – 0x61FF FFFF | 2MB (x13) | Reserved - On-Board Expansion  |

| 0x6200 0000 – 0x62FF FFFF | 1MB (x16) | Reserved - Off-Board Expansion |

| 0x6300 0000 – 0x63FF FFFF | 1MB (x16) | Open - Available for User      |

# 4.2.3 Chip Select 5 (CS7)—CPLD Peripherals (fast timing)

The table below indicates how the CPLD decodes chip select 7. For more detailed information see the *LH7A404-11 IO Controller Specification*.

| Address Range             | Size      | Memory Block Description        |

|---------------------------|-----------|---------------------------------|

| 0x7000 0000 – 0x701F FFFF | 2MB       | Wired LAN Chip Select           |

| 0x7020 0000 – 0x703F FFFF | 2MB       | Card Engine Control Reg         |

| 0x7040 0000 – 0x705F FFFF | 2MB       | Reserved                        |

| 0x7060 0000 – 0x707F FFFF | 2MB       | Reserved                        |

| 0x7080 0000 – 0x709F FFFF | 2MB       | Reserved                        |

| 0x70A0 0000 – 0x70BF FFFF | 2MB       | EEPROM SPI Reg                  |

| 0x70C0 0000 – 0x70DF FFFF | 2MB       | Interrupt/Mask Reg              |

| 0x70E0 0000 – 0x70FF FFFF | 2MB       | Mode Reg                        |

| 0x7100 0000 – 0x711F FFFF | 2MB       | FLASH Reg                       |

| 0x7120 0000 – 0x713F FFFF | 2MB       | Power Management Reg            |

| 0x7140 0000 – 0x715F FFFF | 2MB       | IO Controller Code Revision Reg |

| 0x7160 0000 – 0x717F FFFF | 2MB       | Extended GPIO Reg               |

| 0x7180 0000 – 0x719F FFFF | 2MB       | GPIO Data Reg                   |

| 0x71A0 0000 – 0x71BF FFFF | 2MB       | GPIO Direction Reg              |

| 0x71C0 0000 – 0x71FF FFFF | 2MB (X2)  | Reserved - On-Board Expansion   |

| 0x7200 0000 – 0x72FF FFFF | 1MB (X16) | Reserved - Off-Board Expansion  |

| 0x7300 0000 – 0x73FF FFFF | 1MB (X16) | Open – Available for User       |

# 5 Pin Descriptions & Functions

**IMPORTANT NOTE:** The following pin descriptions and states are described after the initialization of the LogicLoader<sup>™</sup> (bootloader). Many of the signals defined in the tables below can be configured as input or outputs—all GPIOs on the LH7A404 can be configured as either inputs or outputs—or active low/high, and have different functions. It is critical to review all signals in the final design (both electrical and software) to verify the necessary configuration (external pull ups/pull downs).

In addition, keep in mind that the following mode line numbers on the Card Engine do not necessarily line up with the mode line numbers on the processor.

# 5.1 J1C Connector SODIMM 144-Pin Descriptions

| J1C  |                  |     |                                                                                                                                                     |

|------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin# | Signal Name      | 1/0 | Description                                                                                                                                         |

|      |                  |     | This input pair receives 10/100 MB/s Manchester encoded data from the                                                                               |

| 1    | ETHER_RX(-)      | ı   | 10/100 BASE-T receive lines. Route as differential pair with ETHER_RX(+).                                                                           |

|      |                  |     | Active Low. Driven low during power on in order to initiate a hard reset,                                                                           |

|      |                  |     | erasing the contents of external memory. Refer to the reset description                                                                             |

|      |                  |     | found in section 3.2.1 for more information on how this signal is driven.                                                                           |

|      |                  |     | Drives the processor's nPOR line and every peripheral on the Card Engine with a reset line is reset with the assertion of this signal. Refer to the |

|      |                  |     | processor datasheet for register power-on reset states. This signal is pulled                                                                       |

| 2    | MSTR nRST        | ı   | up to 3.3V_uP_SDRAM through a 10K resistor.                                                                                                         |

|      | MOTIC_IIICOT     | •   | This input pair receives 10/100 MB/s Manchester encoded data from the                                                                               |

| 3    | ETHER RX(+)      | ı   | 10/100 BASE-T receive lines. Route as differential pair with ETHER RX(-).                                                                           |

|      |                  | -   | Active Low. This signal initiates a soft reset (manual reset) – external                                                                            |

|      |                  |     | memory contents are retained during reset. Drives processor's nURESET                                                                               |

|      |                  |     | line. Supporting software must be implemented in order to function properly.                                                                        |